LOGIC DESIGN LABORATORY MANUAL

# EXPERIMENT: 1 LOGIC GATES

<u>AIM:</u> To study and verify the truth table of logic gates

#### LEARNING OBJECTIVE:

• Identify various ICs and their specification.

#### COMPONENTS REQUIRED:

- Logic gates (IC) trainer kit.

- Connecting patch chords.

- IC 7400, IC 7408, IC 7432, IC 7406, IC 7402, IC 7404, IC 7486

#### THEORY:

The basic logic gates are the building blocks of more complex logic circuits. These logic gates perform the basic Boolean functions, such as AND, OR, NAND, NOR, Inversion, Exclusive-OR, Exclusive-NOR. Fig. below shows the circuit symbol, Boolean function, and truth. It is seen from the Fig that each gate has one or two binary inputs, A and B, and one binary output, C. The small circle on the output of the circuit symbols designates the logic complement. The AND, OR, NAND, and NOR gates can be extended to have more than two inputs. A gate can be extended to have multiple inputs if the binary operation it represents is commutative and associative.

These basic logic gates are implemented as small-scale integrated circuits (SSICs) or as part of more complex medium scale (MSI) or very large-scale (VLSI) integrated circuits. Digital IC gates are classified not only by their logic operation, but also the specific logic-circuit family to which they belong. Each logic family has its own basic electronic circuit upon which more complex digital circuits and functions are developed. The following logic families are the most frequently used.

TTL →Transistor-transistor logic ECL →Emitter-coupled logic MOS →Metal-oxide semiconductor CMOS →Complementary metal-oxide semiconductor

TTL and ECL are based upon bipolar transistors. TTL has a well established popularity among logic families. ECL is used only in systems requiring high-speed operation. MOS and CMOS, are based on field effect transistors. They are widely used in large scale integrated circuits because of their high component density and relatively low power consumption. CMOS logic consumes far less power than MOS logic. There are various commercial integrated circuit chips available. TTL ICs are usually distinguished by numerical designation as the 5400 and 7400 series.

## PROCEDURE:

- 1. Check the components for their working.

- 2. Insert the appropriate IC into the IC base.

- 3. Make connections as shown in the circuit diagram.

- 4. Provide the input data via the input switches and observe the output on output LEDs

| S.NO | GATE     | SYMBOL                                | INPU | JTS | OUTPUT |

|------|----------|---------------------------------------|------|-----|--------|

|      |          |                                       | A    | В   | С      |

| 1.   | NAND IC  | A                                     | 0    | 0   | 1      |

|      | 7400     | A<br>B $C = \overline{A}\overline{B}$ | 0    | 1   | 1      |

|      |          | ▶                                     | 1    | 0   | 1      |

|      |          |                                       | 1    | 1   | 0      |

| 2.   | NOR IC   | 1                                     | 0    | 0   | 1      |

|      | 7402     | $A$ $C = \overline{A} + \overline{B}$ | 0    | 1   | 0      |

|      |          | в                                     | 1    | 0   | 0      |

|      |          |                                       | 1    | 1   | 0      |

| 3.   | AND IC   |                                       | 0    | 0   | 0      |

|      | 7408     | AC=AB                                 | 0    | 1   | 0      |

|      |          | В                                     | 1    | 0   | 0      |

|      |          |                                       | 1    | 1   | 1      |

| 4.   | OR       | 6                                     | 0    | 0   | 0      |

|      | IC 7432  | A C=A+B                               | 0    | 1   | 1      |

|      |          | в)                                    | 1    | 0   | 1      |

|      |          |                                       | 1    | 1   | 1      |

| 5.   | NOT      | AC=Ā                                  | 1    | -   | 0      |

|      | IC 7404  | · · · · · · · · · · · · · · · · · · · | 0    | -   | 1      |

| б.   | EX-OR IC |                                       | 0    | 0   | 0      |

|      | 7486     | A                                     | 0    | 1   | 1      |

|      |          | )) )                                  | 1    | 0   | 1      |

|      |          | вС=АБ+ВА                              | 1    | 1   | 0      |

|      |          |                                       |      |     |        |

#### **VIVA QUESTIONS:**

- 1. Why NAND & NOR gates are called universal gates?

- 2. Realize the EX OR gates using minimum number of NAND gates.

- 3. Give the truth table for EX-NOR and realize using NAND gates?

- 4. What are the logic low and High levels of TTL IC's and CMOS IC's?

- 5. Compare TTL logic family with CMOS family?

- 6. Which logic family is fastest and which has low power dissipation?

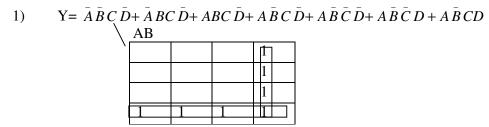

# **EXPERIMENT: 2 REALIZATION OF A BOOLEAN FUNCTION.**

<u>AIM:</u> To simplify the given expression and to realize it using Basic gates and Universal gates

#### **LEARNING OBJECTIVE:**

- To simplify the Boolean expression and to build the logic circuit.

- Given a Truth table to derive the Boolean expressions and build the logic circuit to realize it.

#### **COMPONENTS REQUIRED:**

IC 7400, IC 7408, IC 7432, IC 7406, IC 7402, Patch Cords & IC Trainer Kit.

#### THEORY:

*Canonical Forms (Normal Forms):* Any Boolean function can be written in disjunctive normal form (sum of min-terms) or conjunctive normal form (product of max-terms).

A Boolean function can be represented by a Karnaugh map in which each cell corresponds to a minterm. The cells are arranged in such a way that any two immediately adjacent cells correspond to two minterms of distance 1. There is more than one way to construct a map with this property.

#### Karnaugh Maps

For a function of two variables, say, f(x, y),

|    | X'     | Х      |

|----|--------|--------|

| y' | f(0,0) | f(1,0) |

| у  | f(0,1) | f(1,1) |

For a function of three variables, say, f(x, y, z)

|    | x'y'     | x'y      | ху       | xy'      |

|----|----------|----------|----------|----------|

| z' | f(0,0,0) | f(0,1,0) | f(1,1,0) | f(1,0,0) |

| z  | f(0,0,1) | f(0,1,1) | f(1,1,1) | f(1,0,1) |

For a function of four variables: f(w, x, y, z)

|      | w'x' w'x |   | WX | wx' |

|------|----------|---|----|-----|

| y'z' | 0        | 4 | 12 | 8   |

| y'z  | 1        | 5 | 13 | 9   |

| yz   | 3        | 7 | 15 | 11  |

| yz'  | 2        | 6 | 14 | 10  |

Realization of Boolean expression:

After simplifying using K-Map method we get

$$Y = A\bar{B} + C\bar{D}$$

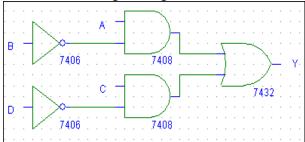

Realization using Basic gates

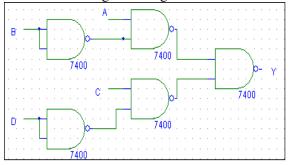

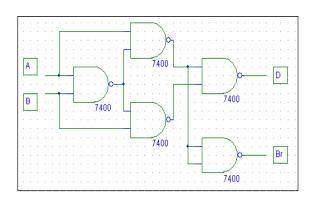

#### Realization using NAND gates

**TRUTH TABLE**

|   | INP | UTS |   | OUTPUT |

|---|-----|-----|---|--------|

| Α | В   | С   | D | Y      |

| 0 | 0   | 0   | 0 | 0      |

| 0 | 0   | 0   | 1 | 0      |

| 0 | 0   | 1   | 0 | 1      |

| 0 | 0   | 1   | 1 | 0      |

| 0 | 1   | 0   | 0 | 0      |

| 0 | 1   | 0   | 1 | 0      |

| 0 | 1   | 1   | 0 | 1      |

| 0 | 1   | 1   | 1 | 0      |

| 1 | 0   | 0   | 0 | 1      |

| 1 | 0   | 0   | 1 | 1      |

| 1 | 0   | 1   | 0 | 1      |

| 1 | 0   | 1   | 1 | 1      |

| 1 | 1   | 0   | 0 | 0      |

| 1 | 1   | 0   | 1 | 0      |

| 1 | 1   | 1   | 0 | 1      |

| 1 | 1   | 1   | 1 | 0      |

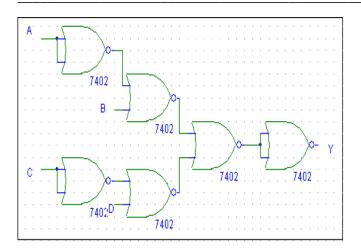

Realization using NOR gates

2) For the given Truth Table, realize a logical circuit using basic gates and NAND gates

|   | Inputs |   |   |   |  |  |

|---|--------|---|---|---|--|--|

| Α | В      | С | D | Y |  |  |

| 0 | 0      | 0 | 0 | 1 |  |  |

| 0 | 0      | 0 | 1 | 1 |  |  |

| 0 | 0      | 1 | 0 | 0 |  |  |

| 0 | 0      | 1 | 1 | 0 |  |  |

| 0 | 1      | 0 | 0 | 1 |  |  |

| 0 | 1      | 0 | 1 | 1 |  |  |

| 0 | 1      | 1 | 0 | 0 |  |  |

| 0 | 1      | 1 | 1 | 0 |  |  |

| 1 | 0      | 0 | 0 | 0 |  |  |

| 1 | 0      | 0 | 1 | 0 |  |  |

| 1 | 0      | 1 | 0 | 0 |  |  |

| 1 | 0      | 1 | 1 | 0 |  |  |

| 1 | 1      | 0 | 0 | 0 |  |  |

| 1 | 1      | 0 | 1 | 1 |  |  |

| 1 | 1      | 1 | 0 | 0 |  |  |

| 1 | 1      | 1 | 1 | 1 |  |  |

#### PROCEDURE:

Check the components for their working.

Insert the appropriate IC into the IC base.

Make connections as shown in the circuit diagram.

Provide the input data via the input switches and observe the output on output LEDs Verify the Truth Table

**<u>RESULT</u>**: Simplified and verified the Boolean function using basic gates and universal gates

#### VIVA QUESTIONS:

- 1) What are the different methods to obtain minimal expression?

- 2) What is a Min term and Max term

- 3) State the difference between SOP and POS.

- 4) What is meant by canonical representation?

- 5) What is K-map? Why is it used?

- 6) What are universal gates?

# **EXPERIMENT: 3** ADDERS AND SUBTRACTORS

#### AIM: To realize

i) Half Adder and Full Adder

ii) Half Subtractor and Full Subtractor by using Basic gates and NAND gates

#### LEARNING OBJECTIVE:

- To realize the adder and subtractor circuits using basic gates and universal gates

- To realize full adder using two half adders

- To realize a full subtractor using two half subtractors

#### COMPONENTS REQUIRED:

IC 7400, IC 7408, IC 7486, IC 7432, Patch Cords & IC Trainer Kit.

#### THEORY:

*Half-Adder:* A combinational logic circuit that performs the addition of two data bits, A and B, is called a half-adder. Addition will result in two output bits; one of which is the sum bit, S, and the other is the carry bit, C. The Boolean functions describing the half-adder are:  $S = A \oplus B$  C = A B

*Full-Adder:* The half-adder does not take the carry bit from its previous stage into account. This carry bit from its previous stage is called carry-in bit. A combinational logic circuit that adds two data bits, A and B, and a carry-in bit, Cin, is called a full-adder. The Boolean functions describing the full-adder are:

$S = (x \oplus y) \oplus Cin$   $C = xy + Cin (x \oplus y)$

*Half Subtractor:* Subtracting a single-bit binary value B from another A (i.e. A -B) produces a difference bit D and a borrow out bit B-out. This operation is called half subtraction and the circuit to realize it is called a half subtractor. The Boolean functions describing the half-Subtractor are:

$S = A \oplus B$  C = A' B

*Full Subtractor:* Subtracting two single-bit binary values, B, Cin from a single-bit value A produces a difference bit D and a borrow out Br bit. This is called full subtraction. The Boolean functions describing the full-subtracter are:

$D = (x \oplus y) \oplus Cin$  Br = A'B + A'(Cin) + B(Cin)

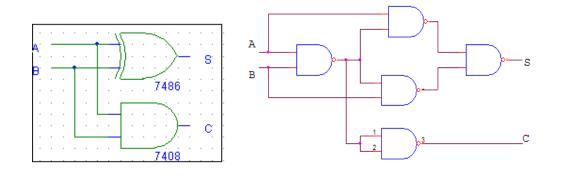

## I. TO REALIZE HALF ADDER

## **TRUTH TABLE**

| INPU | UTS | OUT | PUTS |

|------|-----|-----|------|

| A    | В   | S   | С    |

| 0    | 0   | 0   | 0    |

| 0    | 1   | 1   | 0    |

| 1    | 0   | 1   | 0    |

| 1    | 1   | 0   | 1    |

i) Basic Gates

# **BOOLEAN EXPRESSIONS:**

$S=A \oplus B$ C=A B

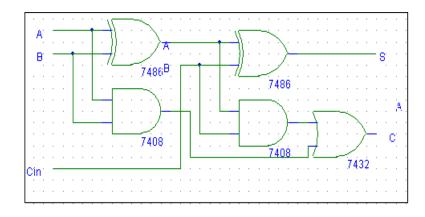

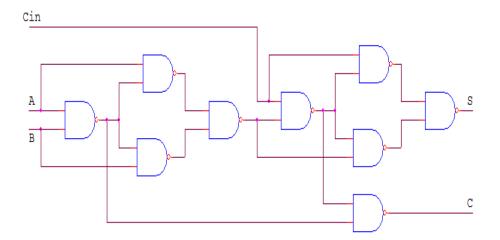

#### II. FULL ADDER

#### **TRUTH TABLE**

| Ι | NPUT  | OUT | PUTS |   |

|---|-------|-----|------|---|

| Α | B Cin |     | S    | С |

| 0 | 0     | 0   | 0    | 0 |

| 0 | 0     | 1   | 1    | 0 |

| 0 | 1     | 0   | 1    | 0 |

| 0 | 1     | 1   | 0    | 1 |

| 1 | 0     | 0   | 1    | 0 |

| 1 | 0     | 1   | 0    | 1 |

| 1 | 1     | 0   | 0    | 1 |

| 1 | 1     | 1   | 1    | 1 |

## **BOOLEAN EXPRESSIONS:**

$S=A \oplus B \oplus C$

## C=A B + B Cin + A Cin

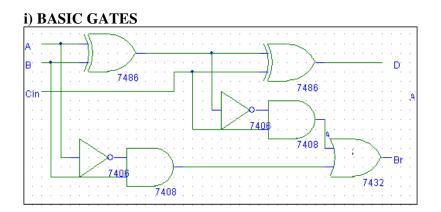

## i)BASIC GATES

ii) NAND GATES

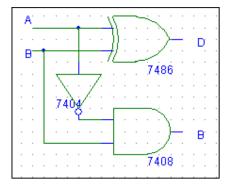

## III. HALF SUBTRACTOR

#### **TRUTH TABLE**

| INPUTS |     | OUTPUTS |    |

|--------|-----|---------|----|

| А      | A B |         | Br |

| 0      | 0   | 0       | 0  |

| 0      | 1   | 1       | 1  |

| 1      | 0   | 1       | 0  |

| 1      | 1   | 0       | 0  |

#### **BOOLEAN EXPRESSIONS:**

$$\mathbf{D} = \mathbf{A} \oplus \mathbf{B}$$

$$\mathbf{Br} = \bar{A}B$$

#### ii) NAND Gates

# IV. FULL SUBTRACTOR

## **TRUTH TABLE**

| Ι | NPUT | OUT | PUTS |    |

|---|------|-----|------|----|

| А | В    | Cin | D    | Br |

| 0 | 0    | 0   | 0    | 0  |

| 0 | 0    | 1   | 1    | 1  |

| 0 | 1    | 0   | 1    | 1  |

| 0 | 1    | 1   | 0    | 1  |

| 1 | 0    | 0   | 1    | 0  |

| 1 | 0    | 1   | 0    | 0  |

| 1 | 1    | 0   | 0    | 0  |

| 1 | 1    | 1   | 1    | 1  |

## **BOOLEAN EXPRESSIONS:**

$\mathbf{D} = \mathbf{A} \oplus \mathbf{B} \oplus \mathbf{C}$  $\mathbf{B} = \bar{A} \mathbf{B} + \mathbf{B} \mathbf{C} \mathbf{i} \mathbf{n} + \bar{A} \mathbf{C} \mathbf{i} \mathbf{n}$

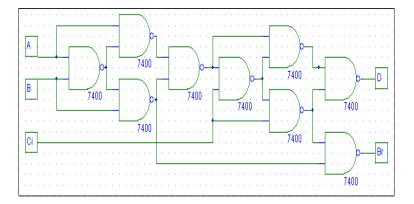

## ii) To Realize the Full subtractor using NAND Gates only

#### PROCEDURE:

- Check the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Verify the Truth Table and observe the outputs.

<u>**RESULT:</u>** The truth table of the above circuits is verified.</u>

#### VIVA QUESTIONS:

- 1) What is a half adder?

- 2) What is a full adder?

- 3) What are the applications of adders?

- 4) What is a half subtractor?

- 5) What is a full subtractor?

- 6) What are the applications of subtractors?

- 7) Obtain the minimal expression for above circuits.

- 8) Realize a full adder using two half adders

- 9) Realize a full subtractors using two half subtractors

## EXPERIMENT: 4 PARALLEL ADDER AND SUBTRACTOR

AIM: To design and set up the following circuit using IC 7483.

- i) A 4-bit binary parallel adder.

- ii) A 4-bit binary parallel subtractor.

#### **LEARNING OBJECTIVE:**

- To learn about IC 7483 and its internal structure.

- To realize a subtractor using adder IC 7483

#### **COMPONENTS REQUIRED:**

IC 7483, IC 7486, Patch Cords & IC Trainer Kit.

#### THEORY:

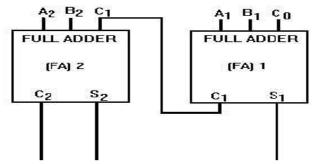

The Full adder can add single-digit binary numbers and carries. The largest sum that can be obtained using a full adder is  $11_2$ . Parallel adders can add multiple-digit numbers. If full adders are placed in parallel, we can add two- or four-digit numbers or any other size desired. Figure below uses STANDARD SYMBOLS to show a parallel adder capable of adding two, two-digit binary numbers The addend would be on A inputs, and the augend on the B inputs. For this explanation we will assume there is no input to C<sub>0</sub> (carry from a previous circuit)

To add  $10_2$  (addend) and  $01_2$  (augend), the addend inputs will be 1 on A2 and 0 on A1. The augend inputs will be 0 on B2 and 1 on B1. Working from right to left, as we do in normal addition, let's calculate the outputs of each full adder. With A1 at 0 and B1 at 1, the output of adder1 will be a sum (S<sub>1</sub>) of 1 with no carry (C<sub>1</sub>). Since A2 is 1 and B2 is 0, we have a sum (S<sub>2</sub>) of 1 with no carry (C<sub>2</sub>) from adder1. To determine the sum, read the outputs (C2, S2, and S1) from left to right. In this case, C2 = 0, S2 = 1, and S1 = 1. The sum, then, of  $10_2$  and  $01_2$

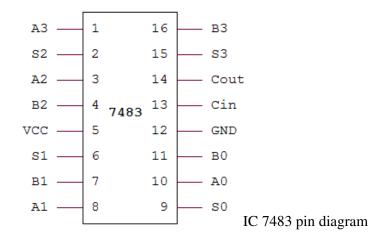

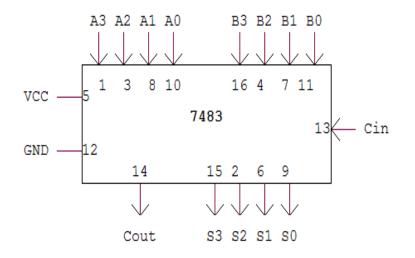

is  $011_2$ . To add four bits we require four full adders arranged in parallel. IC 7483 is a 4- bit parallel adder whose pin diagram is shown.

|        | MSB  |                       |                       |                       | LSB            |

|--------|------|-----------------------|-----------------------|-----------------------|----------------|

|        |      |                       |                       |                       | Cin            |

| INPUTS |      | A <sub>3</sub>        | A <sub>2</sub>        | $A_1$                 | $A_0$          |

|        |      | <b>B</b> <sub>3</sub> | <b>B</b> <sub>2</sub> | <b>B</b> <sub>1</sub> | $B_0$          |

| OUTPUT | Cout | <b>S</b> <sub>3</sub> | <b>S</b> <sub>2</sub> | $S_1$                 | S <sub>0</sub> |

i) 4-Bit Binary Adder

An Example: 7+2=11 (1001)

- 7 is realized at  $A_3 A_2 A_1 A_0 = 0111$

- 2 is realized at  $B_3 B_2 B_1 B_0 = \underline{0010}$ Sum =  $\underline{1001}$

ADDER CIRCUIT:

## PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Apply augend and addend bits on A and B and cin=0.

- Verify the results and observe the outputs.

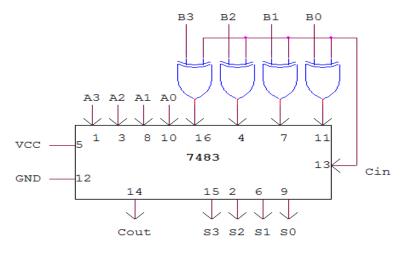

# ii) 4-BIT BINARY SUBTRACTOR.

Subtraction is carried out by adding 2's complement of the subtrahend. Example: 8 - 3 = 5 (0101)

- 8 is realized at  $A_3 A_2 A_1 A_0 = 1000$

- 3 is realized at  $B_3 B_2 B_1 B_0$  through X-OR gates = 0011

- Output of X-OR gate is 1's complement of 3 = 1100

- 2's Complement can be obtained by adding Cin = 1

Therefore

$$\begin{array}{rl} {Cin = & 1} \\ {A_3 \, A_2 \, A_1 \, A_0 = 1 \ 0 \ 0 \ 0} \\ {B_3 \, B_2 \, B_1 \, B_0 = 1 \ 1 \ 0 \ 0} \\ {S_3 \ S2 \ S1 \ S_0 = 0 \ 1 \ 0 \ 1} \\ {Cout = 1 \ (Ignored)} \end{array}$$

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Apply Minuend and subtrahend bits on A and B and cin=1.

- Verify the results and observe the outputs.

<u>RESULTS:</u> Verified the working of IC 7483 as adder and subtractor.

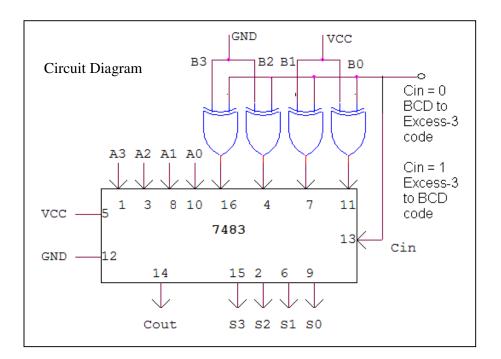

# **EXPERIMENT: 5 BCD TO EXCESS- 3 CODE CONVERTERS.**

AIM: To design and realize the following using IC 7483.

- I) BCD to Excess- 3 Code

- II) Excess-3 to BCD Code.

#### LEARNING OBJECTIVE:

- To learn to realize BCD to Excess-3 code using adder IC 7483

- To learn to realize Excess-3 to BCD Code using adder IC 7483

#### COMPONENTS REQUIRED:

IC 7483, IC 7486, Patch Cords & IC Trainer Kit.

#### THEORY:

Code converter is a combinational circuit that translates the input code word into a new corresponding word. The excess-3 code digit is obtained by adding three to the corresponding BCD digit. To Construct a BCD-to-excess-3-code converter with a 4-bit adder feed BCD-code to the 4-bit adder as the first operand and then feed constant 3 as the second operand. The output is the corresponding excess-3 code.

To make it work as a excess-3 to BCD converter, we feed excess-3 code as the first operand and then feed 2's complement of 3 as the second operand. The output is the BCD code.

ii)

## TRUTH TABLE:

## i) BCD - EXCESS-3 CODE

EXCESS-3 TO BCD CODE

|   | BCD |   |   |   | EX | <b>K-3</b> |   |

|---|-----|---|---|---|----|------------|---|

| 0 | 0   | 0 | 0 | 0 | 0  | 1          | 1 |

| 0 | 0   | 0 | 1 | 0 | 1  | 0          | 0 |

| 0 | 0   | 1 | 0 | 0 | 1  | 0          | 1 |

| 0 | 0   | 1 | 1 | 0 | 1  | 1          | 0 |

| 0 | 1   | 0 | 0 | 0 | 1  | 1          | 1 |

| 0 | 1   | 0 | 1 | 1 | 0  | 0          | 0 |

| 0 | 1   | 1 | 0 | 1 | 0  | 0          | 1 |

| 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

|   | EX-3 |   |   |   | BCD |   |   |  |

|---|------|---|---|---|-----|---|---|--|

| 0 | 0    | 1 | 1 | 0 | 0   | 0 | 0 |  |

| 0 | 1    | 0 | 0 | 0 | 0   | 0 | 1 |  |

| 0 | 1    | 0 | 1 | 0 | 0   | 1 | 0 |  |

| 0 | 1    | 1 | 0 | 0 | 0   | 1 | 1 |  |

| 0 | 1    | 1 | 1 | 0 | 1   | 0 | 0 |  |

| 1 | 0    | 0 | 0 | 0 | 1   | 0 | 1 |  |

| 1 | 0    | 0 | 1 | 0 | 1   | 1 | 0 |  |

| 1 | 0    | 1 | 0 | 0 | 1   | 1 | 1 |  |

| 1 | 0    | 1 | 1 | 1 | 0   | 0 | 0 |  |

| 1 | 1    | 0 | 0 | 1 | 0   | 0 | 1 |  |

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Apply BCD code as first operand(A) and binary 3 as second operand(B) and cin=0 for

#### Realizing BCD-to-Excess-3-code:

- Apply Excess-3-code code as first operand(A) and binary 3 as second operand(B) and Cin=1 for realizing Excess-3-code to BCD.

- Verify the Truth Table and observe the outputs.

RESULT: Realized BCD code to Excess-3 code conversion and vice versa using 7483 IC

#### **VIVA QUESTIONS:**

- 1) What is the internal structure of 7483 IC?

- 2) What do you mean by code conversion?

- 3) What are the applications of code conversion?

- 4) How do you realize a subtractor using full adder?

- 5) What is a ripple Adder? What are its disadvantages?

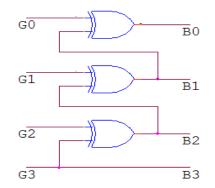

# **EXPERIMENT: 6 BINARY TO GRAY CODE CONVERTER**

AIM: To realize Binary to Gray code converter and vice versa.

#### **LEARNING OBJECTIVE:**

- To learn the importance of non-weighted code

- To learn to generate gray code

#### **COMPONENTS REQUIRED:**

IC 7400, IC 7486, and IC 7408, Patch Cords & IC Trainer Kit

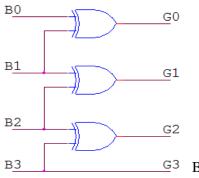

## I) BINARY TO GRAY CONVERSION

| 0 | 0 | 1 | 1 |

|---|---|---|---|

| 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 |

|   |   |   |   |

| 0 | 1 | 0 | 1 |  |

|---|---|---|---|--|

| 0 | 1 | 0 | 1 |  |

| 0 | 1 | 0 | 1 |  |

| 0 | 1 | 0 | 1 |  |

| 0 | 1 | 1 | 0 |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | Γ |

| 1 | 0 | 0 | 1 |

**G3 =** B3

| G2= | B3 | $\oplus$ | B2 |

|-----|----|----------|----|

|     |    |          |    |

G1=B1 ⊕ B2

| 0 | 0 | 0 | 0 |

|---|---|---|---|

| 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 |

G0=B1 ⊕ B0

BOOLEAN EXPRESSIONS: G3=B3 G2=B3 ⊕ B2 G1=B1 ⊕ B2; G0=B1 ⊕ B0

|           | Binary    |           |           |           | Gr | ay |    |

|-----------|-----------|-----------|-----------|-----------|----|----|----|

| <b>B3</b> | <b>B2</b> | <b>B1</b> | <b>B0</b> | <b>G3</b> | G2 | G1 | G0 |

| 0         | 0         | 0         | 0         | 0         | 0  | 0  | 0  |

| 0         | 0         | 0         | 1         | 0         | 0  | 0  | 1  |

| 0         | 0         | 1         | 0         | 0         | 0  | 1  | 1  |

| 0         | 0         | 1         | 1         | 0         | 0  | 1  | 0  |

| 0         | 1         | 0         | 0         | 0         | 1  | 1  | 0  |

| 0         | 1         | 0         | 1         | 0         | 1  | 1  | 1  |

| 0         | 1         | 1         | 0         | 0         | 1  | 0  | 1  |

| 0         | 1         | 1         | 1         | 0         | 1  | 0  | 0  |

| 1         | 0         | 0         | 0         | 1         | 1  | 0  | 0  |

| 1         | 0         | 0         | 1         | 1         | 1  | 0  | 1  |

| 1         | 0         | 1         | 0         | 1         | 1  | 1  | 1  |

| 1         | 0         | 1         | 1         | 1         | 1  | 1  | 0  |

| 1         | 1         | 0         | 0         | 1         | 0  | 1  | 0  |

| 1         | 1         | 0         | 1         | 1         | 0  | 1  | 1  |

| 1         | 1         | 1         | 0         | 1         | 0  | 0  | 1  |

| 1         | 1         | 1         | 1         | 1         | 0  | 0  | 0  |

## G<sup>3</sup> BINARY TO GRAY CODE USING EX-OR GATES

**REALIZATION USING NAND GATES:**

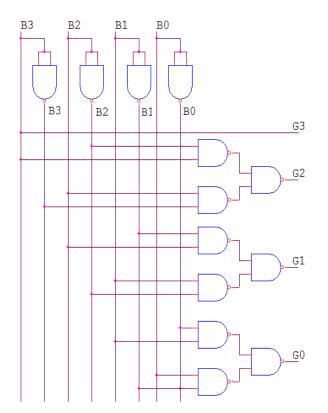

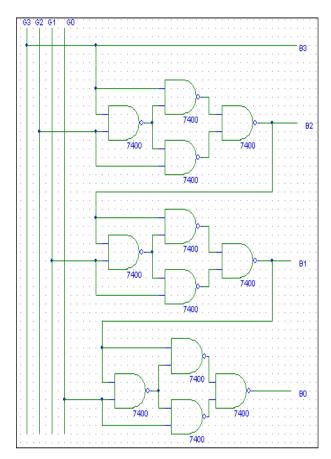

## **II) GRAY TO BINARY CONVERSION**

| 0  | 0 | 1 | 1 |           |

|----|---|---|---|-----------|

| 0  | 0 | 1 | 1 |           |

| 0  | 0 | 1 | 1 |           |

| .0 | 0 | 1 | 1 | = B3 = G3 |

| 0 | 1 | 0 | 1 |                   |

|---|---|---|---|-------------------|

| 0 | 1 | 0 | 1 | -                 |

| 0 | 1 | 0 | 1 | $B2=G3 \oplus G2$ |

| 0 | 1 | 0 | 1 |                   |

| 0 | 1 | 0 | 1 |                               |

|---|---|---|---|-------------------------------|

| 0 | 1 | 0 | 1 | B1=G3 $\oplus$ G2 $\oplus$ G1 |

| 1 | 0 | 1 | 0 |                               |

| 1 | 0 | 1 | 0 |                               |

| 0 | 1 | 0 | 1 |

|---|---|---|---|

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

$\begin{array}{c} \text{B0=G3} \ \oplus \ \text{G2} \oplus \ \text{G1} \oplus \\ \text{G0} \end{array}$

# **BOOLEAN EXPRESSIONS:**

B3=G3 B2=G3  $\oplus$  G2 B1=G3  $\oplus$  G2  $\oplus$  G1 B0=G3  $\oplus$  G2  $\oplus$  G1  $\oplus$  G0

|    | Gray |    |    |    | Bin | ary        |    |

|----|------|----|----|----|-----|------------|----|

| G3 | G2   | G1 | G0 | B3 | B2  | <b>B</b> 1 | B0 |

| 0  | 0    | 0  | 0  | 0  | 0   | 0          | 0  |

| 0  | 0    | 0  | 1  | 0  | 0   | 0          | 1  |

| 0  | 0    | 1  | 1  | 0  | 0   | 1          | 0  |

| 0  | 0    | 1  | 0  | 0  | 0   | 1          | 1  |

| 0  | 1    | 1  | 0  | 0  | 1   | 0          | 0  |

| 0  | 1    | 1  | 1  | 0  | 1   | 0          | 1  |

| 0  | 1    | 0  | 1  | 0  | 1   | 1          | 0  |

| 0  | 1    | 0  | 0  | 0  | 1   | 1          | 1  |

| 1  | 1    | 0  | 0  | 1  | 0   | 0          | 0  |

| 1  | 1    | 0  | 1  | 1  | 0   | 0          | 1  |

| 1  | 1    | 1  | 1  | 1  | 0   | 1          | 0  |

| 1  | 1    | 1  | 0  | 1  | 0   | 1          | 1  |

| 1  | 0    | 1  | 0  | 1  | 1   | 0          | 0  |

| 1  | 0    | 1  | 1  | 1  | 1   | 0          | 1  |

| 1  | 0    | 0  | 1  | 1  | 1   | 1          | 0  |

| 1  | 0    | 0  | 0  | 1  | 1   | 1          | 1  |

# GRAY TO BINARY CODE CONVERSION USING EX-OR GATES

## REALIZATION USING NAND GATES:

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Verify the Truth Table and observe the outputs.

<u>RESULT:</u> Binary to gray code conversion and vice versa is realized using EX-OR gates and NAND gates.

#### **VIVA QUESTIONS:**

- 1) What are code converters?

- 2) What is the necessity of code conversions?

- 3) What is gray code?

- 4) Realize the Boolean expressions for

- a) Binary to gray code conversion

- b) Gray to binary code conversion

# EXPERIMENT: 7 MULTIPLEXER AND DEMULTIPLEXER

AIM: To design and set up the following circuit

- 1) To design and set up a 4:1 Multiplexer (MUX) using only NAND gates.

- 2) To design and set up a 1:4 Demultiplexer(DE-MUX) using only NAND gates.

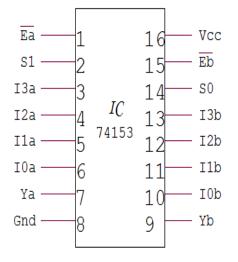

- 3) To verify the various functions of IC 74153(MUX) and IC 74139(DEMUX).

- 4) To set up a Half/Full Adder and Half/Full Subtractor using IC 74153.

#### LEARNING OBJECTIVE:

- To learn about various applications of multiplexer and de-multiplexer

- To learn and understand the working of IC 74153 and IC 74139

- To learn to realize any function using Multiplexer

#### THEORY:

Multiplexers are very useful components in digital systems. They transfer a large number of information units over a smaller number of channels, (usually one channel) under the control of selection signals. Multiplexer means many to one. A multiplexer is a circuit with many inputs but only one output. By using control signals (select lines) we can select any input to the output. Multiplexer is also called as data selector because the output bit depends on the input data bit that is selected. The general multiplexer circuit has  $2^n$  input signals, n control/select signals and 1 output signal.

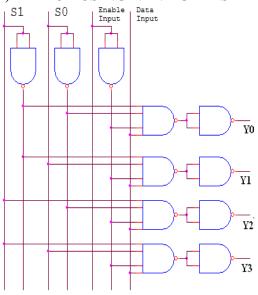

De-multiplexers perform the opposite function of multiplexers. They transfer a small number of information units (usually one unit) over a larger number of channels under the control of selection signals. The general de-multiplexer circuit has 1 input signal, n control/select signals and  $2^n$  output signals. De-multiplexer circuit can also be realized using a decoder circuit with enable.

#### COMPONENTS REQUIRED:

IC 7400, IC 7410, IC 7420, IC 7404, IC 74153, IC 74139, Patch Cords & IC Trainer Kit.

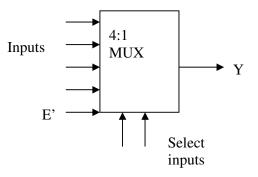

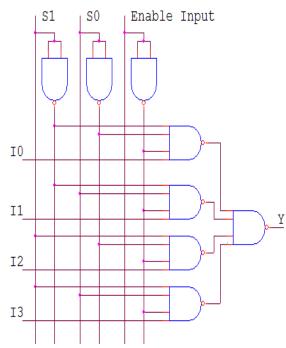

## i) 4:1 MULTIPLEXER

Output Y= E'S1'S0'I0 + E'S1'S0I1 + E'S1S0'I2 + E'S1S0I3

# **REALIZATION USING NAND GATES**

# TRUTH TABLE

| Sel<br>Inp | ect            | Enable<br>Input | Inputs         |                |       | Out<br>puts    |   |

|------------|----------------|-----------------|----------------|----------------|-------|----------------|---|

| $S_1$      | S <sub>0</sub> | E               | I <sub>0</sub> | I <sub>1</sub> | $I_2$ | I <sub>3</sub> | Y |

| Х          | Х              | 1               | Х              | Х              | Х     | Х              | 0 |

| 0          | 0              | 0               | 0              | Х              | Х     | Х              | 0 |

| 0          | 0              | 0               | 1              | Х              | Х     | Х              | 1 |

| 0          | 1              | 0               | Х              | 0              | Х     | Х              | 0 |

| 0          | 1              | 0               | Х              | 1              | Х     | Х              | 1 |

| 1          | 0              | 0               | Х              | Х              | 0     | Х              | 0 |

| 1          | 0              | 0               | Х              | Х              | 1     | Х              | 1 |

| 1          | 1              | 0               | Х              | Х              | Х     | 0              | 0 |

| 1          | 1              | 0               | Х              | Х              | X     | 1              | 1 |

# VERIFY IC 74153 MUX (DUAL 4:1 MULTIPLEXER)

| Enable<br>Inputs | Data<br>Input | Select<br>Inputs      |                | Outputs        |                       |                       |                |

|------------------|---------------|-----------------------|----------------|----------------|-----------------------|-----------------------|----------------|

| Е                | D             | <b>S</b> <sub>1</sub> | S <sub>0</sub> | Y <sub>3</sub> | <b>Y</b> <sub>2</sub> | <b>Y</b> <sub>1</sub> | Y <sub>0</sub> |

| 1                | 0             | Х                     | Х              | Х              | Х                     | Х                     | Х              |

| 0                | 1             | 0                     | 0              | 0              | 0                     | 0                     | 1              |

| 0                | 1             | 0                     | 1              | 0              | 0                     | 1                     | 0              |

| 0                | 1             | 1                     | 0              | 0              | 1                     | 0                     | 0              |

| 0                | 1             | 1                     | 1              | 1              | 0                     | 0                     | 0              |

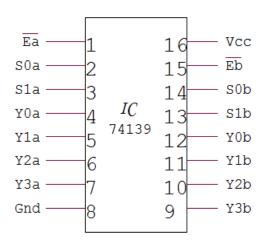

## **VERIFICATION OF IC 74139 (DEMUX)**

|    | Inputs         |                |                | Out            | puts                  |                |

|----|----------------|----------------|----------------|----------------|-----------------------|----------------|

| Ea | S <sub>1</sub> | S <sub>0</sub> | Y <sub>3</sub> | Y <sub>2</sub> | <b>Y</b> <sub>1</sub> | Y <sub>0</sub> |

| 1  | Х              | Х              | 1              | 1              | 1                     | 1              |

| 0  | 0              | 0              | 1              | 1              | 1                     | 0              |

| 0  | 0              | 1              | 1              | 1              | 0                     | 1              |

| 0  | 1              | 0              | 1              | 0              | 1                     | 1              |

| 0  | 1              | 1              | 0              | 1              | 1                     | 1              |

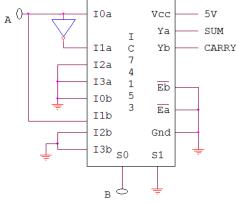

## HALF ADDER USING MUX:

## **DESIGN:**

| SUM |    | CARRY |    |    |

|-----|----|-------|----|----|

| I0  | I1 |       | IO | I1 |

| 0   | 1  |       | 0  | 1  |

| 2   | 3  |       | 2  | 3  |

| Α   | A' |       | 0  | A  |

# **CIRCUIT:**

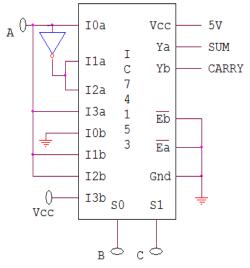

## **FULL ADDER USING MUX:**

#### **DESIGN:**

| SUM |           |           |    |  |  |  |

|-----|-----------|-----------|----|--|--|--|

| IO  | I1        | I3        | I3 |  |  |  |

| 0   | 1         | 2         | 3  |  |  |  |

| 4   | 5         | 6         | 7  |  |  |  |

| Α   | <b>A'</b> | <b>A'</b> | Α  |  |  |  |

#### CARRY I0 I1 I3 I3 0 1 2 3 4 5 6 7

A

1

A

0

# **TRUTH TABLE**

| Inputs |   |   | Outputs |   |  |

|--------|---|---|---------|---|--|

| Α      | В | С | S       | С |  |

| 0      | 0 | 0 | 0       | 0 |  |

| 0      | 0 | 1 | 1       | 0 |  |

| 0      | 1 | 0 | 1       | 0 |  |

| 0      | 1 | 1 | 0       | 1 |  |

| 1      | 0 | 0 | 1       | 0 |  |

| 1      | 0 | 1 | 0       | 1 |  |

| 1      | 1 | 0 | 0       | 1 |  |

| 1      | 1 | 1 | 1       | 1 |  |

| Inputs |   | Outputs |   |  |

|--------|---|---------|---|--|

| Α      | В | S       | С |  |

| 0      | 0 | 0       | 0 |  |

| 0      | 1 | 1       | 0 |  |

| 1      | 0 | 1       | 0 |  |

| 1      | 1 | 0       | 1 |  |

# FULL ADDER CIRCUIT

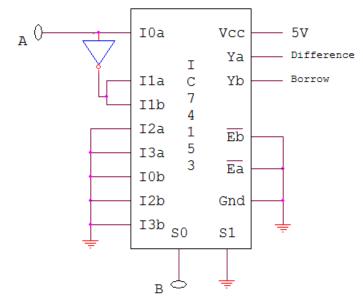

# HALF SUBTRACTOR USING MUX:

DESIGN:

| D | DIFFERENCE |    | BORROW |    |    |

|---|------------|----|--------|----|----|

|   | I0         | I1 |        | I0 | I1 |

|   | 0          | 1  |        | 0  | 1  |

|   | 2          | 3  |        | 2  | 3  |

|   | Α          | A' |        | 0  | A' |

CIRCUIT:

| Inputs |   | Outputs |    |  |

|--------|---|---------|----|--|

| Α      | В | D       | Br |  |

| 0      | 0 | 0       | 0  |  |

| 0      | 1 | 1       | 1  |  |

| 1      | 0 | 1       | 0  |  |

| 1      | 1 | 0       | 0  |  |

## FULL SUBTRACTOR USING MUX:

DESIGN:

| DIFFERENCE |           |           |    |  |  |  |

|------------|-----------|-----------|----|--|--|--|

| IO         | I1        | I2        | I3 |  |  |  |

| 0          | 1         | 2         | 3  |  |  |  |

| 4          | 5         | 6         | 7  |  |  |  |

| Α          | <b>A'</b> | <b>A'</b> | Α  |  |  |  |

BORROW

| IO | I1        | I2 | I3 |

|----|-----------|----|----|

| 0  | 1         | 2  | 3  |

| 4  | 5         | 6  | 7  |

| 0  | <b>A'</b> | A' | 1  |

#### **TRUTH TABLE**

|   | Inputs | Outputs |   |    |  |

|---|--------|---------|---|----|--|

| Α | В      | С       | D | Br |  |

| 0 | 0      | 0       | 0 | 0  |  |

| 0 | 0      | 1       | 1 | 1  |  |

| 0 | 1      | 0       | 1 | 1  |  |

| 0 | 1      | 1       | 0 | 1  |  |

| 1 | 0      | 0       | 1 | 0  |  |

| 1 | 0      | 1       | 0 | 0  |  |

| 1 | 1      | 0       | 0 | 0  |  |

| 1 | 1      | 1       | 1 | 1  |  |

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Verify the Truth Table and observe the outputs.

**RESULT:** Adder and subtractor circuits are realized using multiplexer IC 74153.

#### **VIVA QUESTIONS:**

- 1) What is a multiplexer?

- 2) What is a de-multiplexer?

- 3) What are the applications of multiplexer and de-multiplexer?

- 4) Derive the Boolean expression for multiplexer and de-multiplexer.

- 5) How do you realize a given function using multiplexer

- 6) What is the difference between multiplexer & demultiplexer?

- 7) In 2n to 1 multiplexer how many selection lines are there?

- 8) How to get higher order multiplexers?

- 9) Implement an 8:1 mux using 4:1 muxes?

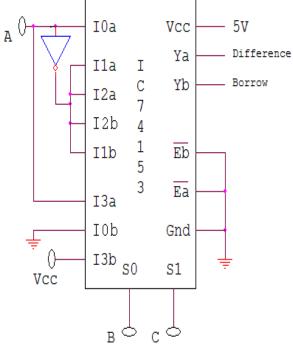

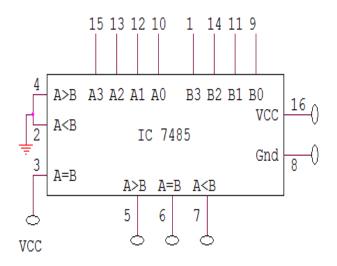

# EXPERIMENT: 8 COMPARATORS

AIM: To realize One & Two Bit Comparator and study of 7485 magnitude comparator.

## LEARNING OBJECTIVE:

- To learn about various applications of comparator

- To learn and understand the working of IC 7485 magnitude comparator

- To learn to realize 8-bit comparator using 4-bit comparator

## THEORY:

Magnitude Comparator is a logical circuit, which compares two signals A and B and generates three logical outputs, whether A > B, A = B, or A < B. IC 7485 is a high speed 4-bit Magnitude comparator, which compares two 4-bit words. The A = B Input must be held high for proper compare operation.

#### **COMPONENTS REQUIRED:**

IC 7400, IC 7410, IC 7420, IC 7432, IC 7486, IC 7402, IC 7408, IC 7404, IC 7485, Patch Cords & IC Trainer Kit.

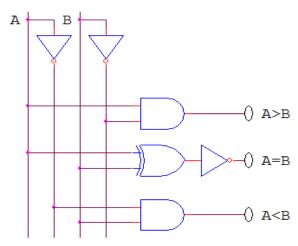

## 1) 1- BIT COMPARATOR

# TRUTH TABLE

$A>B = A \overline{B}$

$A < B = \bar{A} B$

$A=B = \overline{A} \overline{B} + AB$

| INP | UTS | OUTPUTS |                           |       |  |  |  |

|-----|-----|---------|---------------------------|-------|--|--|--|

| Α   | В   | A > B   | $\mathbf{A} = \mathbf{B}$ | A < B |  |  |  |

| 0   | 0   | 0       | 1                         | 0     |  |  |  |

| 0   | 1   | 0       | 0                         | 1     |  |  |  |

| 1   | 0   | 1       | 0                         | 0     |  |  |  |

| 1   | 1   | 0       | 1                         | 0     |  |  |  |

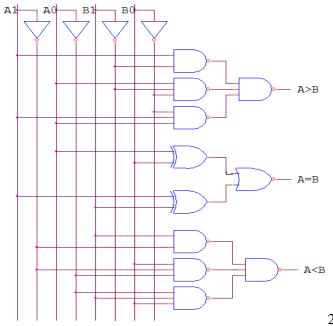

## 2) 2- BIT COMPARATOR

$(A>B) = A1 \overline{B}1 + A0 \overline{B}1 \overline{B}0 + \overline{B}0A1A0$  $(A=B) = (A0 \oplus B0) (A1 \oplus B1)$

$(A < B) = B1 A1 + B0 \overline{A} 1 \overline{A} 0 + \overline{A} 0B 1B 0$

2-bit comparator circuit diagram

|                | INP            | UTS                   |                | OUTPUTS |                           |       |  |

|----------------|----------------|-----------------------|----------------|---------|---------------------------|-------|--|

| A <sub>1</sub> | A <sub>0</sub> | <b>B</b> <sub>1</sub> | B <sub>0</sub> | A > B   | $\mathbf{A} = \mathbf{B}$ | A < B |  |

| 0              | 0              | 0                     | 0              | 0       | 1                         | 0     |  |

| 0              | 0              | 0                     | 1              | 0       | 0                         | 1     |  |

| 0              | 0              | 1                     | 0              | 0       | 0                         | 1     |  |

| 0              | 0              | 1                     | 1              | 0       | 0                         | 1     |  |

| 0              | 1              | 0                     | 0              | 1       | 0                         | 0     |  |

| 0              | 1              | 0                     | 1              | 0       | 1                         | 0     |  |

| 0              | 1              | 1                     | 0              | 0       | 0                         | 1     |  |

| 0              | 1              | 1                     | 1              | 0       | 0                         | 1     |  |

| 1              | 0              | 0                     | 0              | 1       | 0                         | 0     |  |

| 1              | 0              | 0                     | 1              | 1       | 0                         | 0     |  |

| 1              | 0              | 1                     | 0              | 0       | 1                         | 0     |  |

| 1              | 0              | 1                     | 1              | 0       | 0                         | 1     |  |

| 1              | 1              | 0                     | 0              | 1       | 0                         | 0     |  |

| 1              | 1              | 0                     | 1              | 1       | 0                         | 0     |  |

| 1              | 1              | 1                     | 0              | 1       | 0                         | 0     |  |

| 1              | 1              | 1                     | 1              | 0       | 1                         | 0     |  |

## 3) TO COMPARE THE GIVEN DATA USING 7485 CHIP.

| Result                    |           | В         |           |           |    | Α  |    |    |  |  |

|---------------------------|-----------|-----------|-----------|-----------|----|----|----|----|--|--|

|                           | <b>B0</b> | <b>B1</b> | <b>B2</b> | <b>B3</b> | A0 | A1 | A2 | A3 |  |  |

| A > B                     | 0         | 0         | 0         | 0         | 1  | 0  | 0  | 0  |  |  |

| $\mathbf{A} = \mathbf{B}$ | 1         | 0         | 0         | 0         | 1  | 0  | 0  | 0  |  |  |

| A < B                     | 1         | 0         | 0         | 0         | 0  | 0  | 0  | 0  |  |  |

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Verify the Truth Table and observe the outputs.

<u>RESULT:</u> One bit, two bit and four bit comparators are verified using basic gates and magnitude comparator IC7485

#### **VIVA QUESTIONS:**

- 1) What is a comparator?

- 2) What are the applications of comparator?

- 3) Derive the Boolean expressions of one bit comparator and two bit comparators.

- 4) How do you realize a higher magnitude comparator using lower bit comparator

- 5) Design a 2 bit comparator using a single Logic gates?

- 6) Design an 8 bit comparator using a two numbers of IC 7485?

# **EXPERIMENT: 9 DECODERS**

AIM: To realize a decoder circuit using basic gates and to verify IC 74LS139

## LEARNING OBJECTIVE:

- To learn about working principle of decoder

- To learn and understand the working of IC 74LS139

- To realize using basic gates as well as universal gates

#### **COMPONENTS REQUIRED:**

IC74LS139, IC 7400, IC 7408, IC 7432, IC 7404, IC 7410, Patch chords, & IC Trainer Kit

#### THEORY:

A decoder is a combinational circuit that connects the binary information from 'n' input lines to a maximum of  $2^n$  unique output lines. Decoder is also called a min-term generator/maxterm generator. A min-term generator is constructed using AND and NOT gates. The appropriate output is indicated by logic 1 (positive logic). Max-term generator is constructed using NAND gates. The appropriate output is indicated by logic 0 (Negative logic). The IC 74139 accepts two binary inputs and when enable provides 4 individual active low

The IC 74139 accepts two binary inputs and when enable provides 4 individual active low outputs. The device has 2 enable inputs (Two active low).

## **CIRCUIT DIAGRAM:**

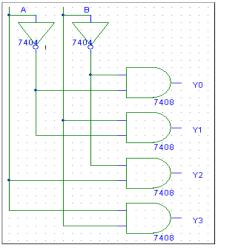

## **2:4 DECODER (MIN TERM GENERATOR):**

## **TRUTH TABLE:**

| INPUT |   | OUT | OUTPUT      |   |   |  |  |  |  |

|-------|---|-----|-------------|---|---|--|--|--|--|

| Α     | B | Y0  | Y0 Y1 Y2 Y3 |   |   |  |  |  |  |

| 0     | 0 | 1   | 0           | 0 | 0 |  |  |  |  |

| 0     | 1 | 0   | 1           | 0 | 0 |  |  |  |  |

| 1     | 0 | 0   | 0           | 1 | 0 |  |  |  |  |

| 1     | 1 | 0   | 0           | 0 | 1 |  |  |  |  |

## **BOOLAEN EXPRESSIONS:**

- $Y0 = \overline{AB}$  $Y1 = \overline{AB}$

- $Y2 = A\overline{B}$

- Y3 = AB

## CIRCUIT DIAGRAM:

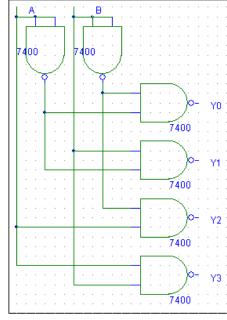

# 2:4 DECODER (MAX TERM GENERATOR):

# **TRUTH TABLE:**

| INPUT |   | OUTPUT |             |   |   |  |  |  |

|-------|---|--------|-------------|---|---|--|--|--|

| Α     | B | Y0     | Y0 Y1 Y2 Y3 |   |   |  |  |  |

| 0     | 0 | 0      | 1           | 1 | 1 |  |  |  |

| 0     | 1 | 1      | 0           | 1 | 1 |  |  |  |

| 1     | 0 | 1      | 1           | 0 | 1 |  |  |  |

| 1     | 1 | 1      | 1           | 1 | 0 |  |  |  |

# **CIRCUIT DIAGRAM:**

STUDY OF IC 74LS139:

#### PROCEDURE:

- 1. Make the connections as per the circuit diagram.

- 2. Change the values of G1, G2A, G2B, A, B, and C, using switches.

- 3. Observe status of Y0, to Y7 on LED's.

- 4. Verify the truth table.

**<u>RESULT</u>**: Verified the Operation of 3 to 8 Decoder

# VIVA QUESTIONS:

- 1. What are the applications of decoder?

- 2. What is the difference between decoder & encoder?

- 3. For n-  $2^n$  decoder how many i/p lines & how many o/p lines?

- 4. What are the different codes & their applications?

- 5. What are code converters?

- 6. Using 3:8 decoder and associated logic, implement a full adder?

- 7. Implement a full subtractor using IC 74138?

- 8. What is the difference between decoder and de-mux?

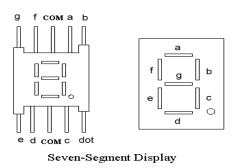

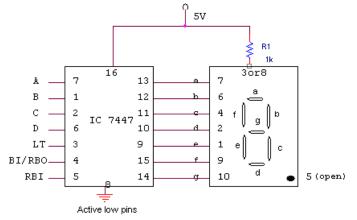

# EXPERIMENT: 10 BCD TO 7-SEGMENT DECODER/DRIVER

AIM: To set up and test a 7-segment static display system to display numbers 0 to 9.

## LEARNING OBJECTIVE:

- To learn about various applications of decoder

- To learn and understand the working of IC 7447

- To learn about types of seven-segment display

#### COMPONENTS REQUIRED:

IC7447, 7-Segment display (common anode), Patch chords, resistor (1KΩ) & IC Trainer Kit

## THEORY:

The Light Emitting Diode (LED) finds its place in many applications in these modern electronic fields. One of them is the Seven Segment Display. Seven-segment displays contains the arrangement of the LEDs in "Eight" (8) passion, and a Dot (.) with a common electrode, lead (Anode or Cathode). The purpose of arranging it in that passion is that we can make any number out of that by switching ON and OFF the particular LED's. Here is the block diagram of the Seven Segment LED arrangement.

The Light Emitting Diode (LED), finds its place in many applications in this modern electronic fields. One of them is the Seven Segment Display. Seven-segment displays contains the arrangement of the LEDs in "Eight" (8) passion, and a Dot (.) with a common electrode, lead (Anode or Cathode). The purpose of arranging it in that passion is that we can make any number out of that by switching ON and OFF the particular LED's. Here is the block diagram of the Seven Segment LED arrangement.

LED's are basically of two types-

Common Cathode (CC) -All the 8 anode legs uses only one cathode, which is common. Common Anode (CA)-The common leg for all the cathode is of Anode type.

A decoder is a combinational circuit that connects the binary information from 'n' input lines to a maximum of  $2^n$  unique output lines. The IC7447 is a BCD to 7-segment pattern converter. The IC7447 takes the Binary Coded Decimal (BCD) as the input and outputs the relevant 7 segment code.

#### CIRCUIT DIAGRAM:

## TRUTH TABLE:

|   | BCD I | nputs |   | Output Logic Levels from IC 7447 to 7-segments |   |   |   |   |   | Decimal<br>number<br>display |   |

|---|-------|-------|---|------------------------------------------------|---|---|---|---|---|------------------------------|---|

| D | C     | В     | А | а                                              | b | с | d | e | f | g                            |   |

| 0 | 0     | 0     | 0 | 0                                              | 0 | 0 | 0 | 0 | 0 | 1                            | 0 |

| 0 | 0     | 0     | 1 | 1                                              | 0 | 0 | 1 | 1 | 1 | 1                            | 1 |

| 0 | 0     | 1     | 0 | 0                                              | 0 | 1 | 0 | 0 | 1 | 0                            | 2 |

| 0 | 0     | 1     | 1 | 0                                              | 0 | 0 | 0 | 1 | 1 | 0                            | 3 |

| 0 | 1     | 0     | 0 | 1                                              | 0 | 0 | 1 | 1 | 0 | 0                            | 4 |

| 0 | 1     | 0     | 1 | 0                                              | 1 | 0 | 0 | 1 | 0 | 0                            | 5 |

| 0 | 1     | 1     | 0 | 1                                              | 1 | 0 | 0 | 0 | 0 | 0                            | 6 |

| 0 | 1     | 1     | 1 | 0                                              | 0 | 0 | 1 | 1 | 1 | 1                            | 7 |

| 1 | 0     | 0     | 0 | 0                                              | 0 | 0 | 0 | 0 | 0 | 0                            | 8 |

| 1 | 0     | 0     | 1 | 0                                              | 0 | 0 | 1 | 1 | 0 | 0                            | 9 |

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Verify the Truth Table and observe the outputs.

#### VIVA QUESTIONS:

- 1. What are the different types of LEDs?

- 2. Draw the internal circuit diagram of an LED.

- 3. What are the applications of LEDs?

## EXPERIMENT: 11 ENCODERS

### AIM:

- 1. To set up a circuit of Decimal-to-BCD Encoder using IC 74147.

- 2. To design and set up a circuit of Hexadecimal-to-Binary Encoder using IC

- 3. 74148 Encoders and IC 74157 Multiplexer

### LEARNING OBJECTIVE:

- To learn about various applications of Encoders

- To learn and understand the working of IC 74147, IC 74148 & IC 74157

- To learn to do code conversion using encoders

#### **COMPONENTS REQUIRED:**

IC 74147, IC 74148, IC 74157, Patch chords & IC Trainer Kit

## THEORY:

An encoder performs a function that is the opposite of decoder. It receives one or more signals in an encoded format and output a code that can be processed by another logic circuit. One of the advantages of encoding data, or more often data addresses in computers, is that it reduces the number of required bits to represent data or addresses. For example, if a memory has 16 different locations, in order to access these 16 different locations, 16 lines (bits) are required if the addressing signals are in 1 out of n format. However, if we code the 16 different addresses

into a binary format, then only 4 lines (bits) are required. Such a reduction improves the speed of information processing in digital systems.

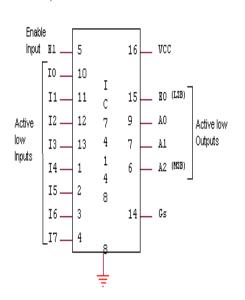

#### CIRCUIT DIAGRAM:

#### **INPUTS OUTPUTS** $I_2$ $I_3$ $I_4$ $I_5$ $I_6$ $I_7$ $I_8$ I9 $A_3$ $A_2$ $A_1$ $A_0$ $I_1$ VCC I1 -I2 \_ Х Х Х Х Х Х Х Ι I3 -Х XX Х Х Х С AO (LSB) Active I4 \_ Х Х Х Х Х low I5 -\_ A1 Active low Х Х Х Х Inputs Outputs - A2 I6 – Х Х Х A3 (MSB) 17 -Х Х I8 \_ Х I9 \_

## 1) DECIMAL-TO BCD ENCODER USING IC 74147. TRUTH TABLE

#### 2) OCTAL TO BINARY ENCODER USING IC 74148.

#### **TRUTH TABLE**

|       | Inputs         |       |       |                |       |                |                |       |                | Outputs |                |    |                |

|-------|----------------|-------|-------|----------------|-------|----------------|----------------|-------|----------------|---------|----------------|----|----------------|

| $E_1$ | I <sub>0</sub> | $I_1$ | $I_2$ | I <sub>3</sub> | $I_4$ | I <sub>5</sub> | I <sub>6</sub> | $I_7$ | A <sub>2</sub> | $A_1$   | A <sub>0</sub> | Gs | E <sub>0</sub> |

| 1     | Χ              | Χ     | Х     | Х              | Х     | Х              | Х              | Х     | 1              | 1       | 1              | 1  | 1              |

| 0     | 1              | 1     | 1     | 1              | 1     | 1              | 1              | 1     | 1              | 1       | 1              | 1  | 0              |

| 0     | Х              | Х     | Х     | Х              | Х     | Х              | Х              | 0     | 0              | 0       | 0              | 0  | 1              |

| 0     | Х              | Х     | Х     | Х              | Х     | Х              | 0              | 1     | 0              | 0       | 1              | 0  | 1              |

| 0     | Х              | Х     | Х     | Х              | Х     | 0              | 1              | 1     | 0              | 1       | 0              | 0  | 1              |

| 0     | Х              | Х     | Х     | Х              | 0     | 1              | 1              | 1     | 0              | 1       | 1              | 0  | 1              |

| 0     | Х              | Х     | Х     | 0              | 1     | 1              | 1              | 1     | 1              | 0       | 0              | 0  | 1              |

| 0     | Х              | Х     | 0     | 1              | 1     | 1              | 1              | 1     | 1              | 0       | 1              | 0  | 1              |

| 0     | Χ              | 0     | 1     | 1              | 1     | 1              | 1              | 1     | 1              | 1       | 0              | 0  | 1              |

| 0     | 0              | 1     | 1     | 1              | 1     | 1              | 1              | 1     | 1              | 1       | 1              | 0  | 1              |

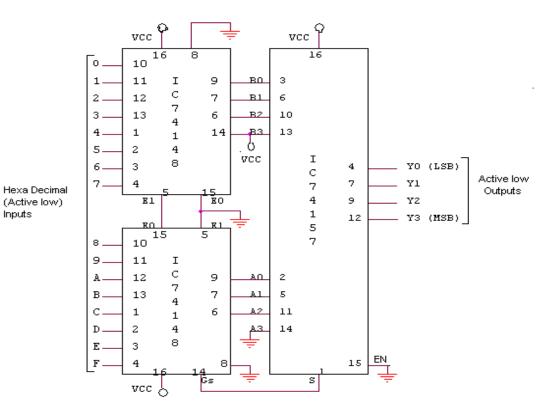

#### 3) HEXADECIMAL TO BINARY ENCODER

|                |       |       |                |                |                |                | IN    | PUT   | S  |                 |                 |                 |                 |                 |                 | (              | DUT                   | PUTS  | 5                     |

|----------------|-------|-------|----------------|----------------|----------------|----------------|-------|-------|----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|-----------------------|-------|-----------------------|

| I <sub>0</sub> | $I_1$ | $I_2$ | I <sub>3</sub> | I <sub>4</sub> | I <sub>5</sub> | I <sub>6</sub> | $I_7$ | $I_8$ | I9 | I <sub>10</sub> | I <sub>11</sub> | I <sub>12</sub> | I <sub>13</sub> | I <sub>14</sub> | I <sub>15</sub> | Y <sub>3</sub> | <b>Y</b> <sub>2</sub> | $Y_1$ | <b>Y</b> <sub>0</sub> |

| 1              | 1     | 1     | 1              | 1              | 1              | 1              | 0     | 1     | 1  | 1               | 1               | 1               | 1               | 1               | 1               | 1              | 0                     | 0     | 0                     |

| 1              | 1     | 1     | 1              | 1              | 1              | 0              | 1     | 1     | 1  | 1               | 1               | 1               | 1               | 1               | 1               | 1              | 0                     | 0     | 1                     |

| 1              | 1     | 1     | 1              | 1              | 0              | 1              | 1     | 1     | 1  | 1               | 1               | 1               | 1               | 1               | 1               | 1              | 0                     | 1     | 0                     |

| 1              | 1     | 1     | 1              | 0              | 1              | 1              | 1     | 1     | 1  | 1               | 1               | 1               | 1               | 1               | 1               | 1              | 0                     | 1     | 1                     |

| 1              | 1     | 1     | 0              | 1              | 1              | 1              | 1     | 1     | 1  | 1               | 1               | 1               | 1               | 1               | 1               | 1              | 1                     | 0     | 0                     |

| 1              | 1     | 0     | 1              | 1              | 1              | 1              | 1     | 1     | 1  | 1               | 1               | 1               | 1               | 1               | 1               | 1              | 1                     | 0     | 1                     |

| 1              | 0     | 1     | 1              | 1              | 1              | 1              | 1     | 1     | 1  | 1               | 1               | 1               | 1               | 1               | 1               | 1              | 1                     | 1     | 0                     |

| 0              | 1     | 1     | 1              | 1              | 1              | 1              | 1     | 1     | 1  | 1               | 1               | 1               | 1               | 1               | 1               | 1              | 1                     | 1     | 1                     |

| 1              | 1     | 1     | 1              | 1              | 1              | 1              | 1     | 1     | 1  | 1               | 1               | 1               | 1               | 1               | 0               | 0              | 0                     | 0     | 0                     |

| 1              | 1     | 1     | 1              | 1              | 1              | 1              | 1     | 1     | 1  | 1               | 1               | 1               | 1               | 0               | 1               | 0              | 0                     | 0     | 1                     |

| 1              | 1     | 1     | 1              | 1              | 1              | 1              | 1     | 1     | 1  | 1               | 1               | 1               | 0               | 1               | 1               | 0              | 0                     | 1     | 0                     |

| 1              | 1     | 1     | 1              | 1              | 1              | 1              | 1     | 1     | 1  | 1               | 1               | 0               | 1               | 1               | 1               | 0              | 0                     | 1     | 1                     |

| 1              | 1     | 1     | 1              | 1              | 1              | 1              | 1     | 1     | 1  | 1               | 0               | 1               | 1               | 1               | 1               | 0              | 1                     | 0     | 0                     |

| 1              | 1     | 1     | 1              | 1              | 1              | 1              | 1     | 1     | 1  | 0               | 1               | 1               | 1               | 1               | 1               | 0              | 1                     | 0     | 1                     |

| 1              | 1     | 1     | 1              | 1              | 1              | 1              | 1     | 1     | 0  | 1               | 1               | 1               | 1               | 1               | 1               | 0              | 1                     | 1     | 0                     |

| 1              | 1     | 1     | 1              | 1              | 1              | 1              | 1     | 0     | 1  | 1               | 1               | 1               | 1               | 1               | 1               | 0              | 1                     | 1     | 1                     |

| 1              | 1     | 1     | 1              | 1              | 1              | 1              | 1     | 1     | 1  | 1               | 1               | 1               | 1               | 1               | 1               | 1              | 1                     | 1     | 1                     |

| 0              | 0     | 0     | 0              | 0              | 0              | 0              | 0     | 0     | 0  | 0               | 0               | 0               | 0               | 0               | 0               | 0              | 0                     | 0     | 0                     |

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Verify the Truth Table and observe the outputs.

#### **VIVA QUESTIONS:**

- 1. What is a priority encoder?

- 2. What is the role of an encoder in communication?

- 3. What is the advantage of using an encoder?

- 4. What are the uses of validating outputs?

## EXPERIMENT: 12 FLIP FLOPS

AIM: Truth Table verification of

- 1) RS Flip Flop

- 2) T type Flip Flop.

- 3) D type Flip Flop.

- 4) JK Flip Flop.

- 5) JK Master Slave Flip Flop.

#### LEARNING OBJECTIVE:

- To learn about various Flip-Flops

- To learn and understand the working of Master slave FF

- To learn about applications of FFs

- Conversion of one type of Flip flop to another

#### COMPONENTS REQUIRED:

IC 7408, IC 7404, IC 7402, IC 7400, Patch Cords & IC Trainer Kit.

#### THEORY:

Logic circuits that incorporate memory cells are called *sequential logic circuits*; their output depends not only upon the present value of the input but also upon the previous values. Sequential logic circuits often require a timing generator (a clock) for their operation. The latch (flip-flop) is a basic bi-stable memory element widely used in sequential logic circuits. Usually there are two outputs, Q and its complementary value. Some of the most widely used latches are listed below.

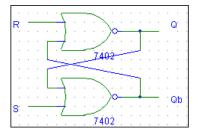

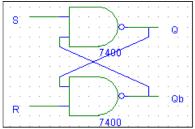

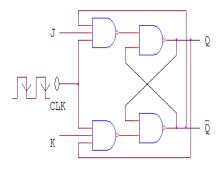

#### SR LATCH:

An S-R latch consists of two cross-coupled NOR gates. An S-R flip-flop can also be design using cross-coupled NAND gates as shown. The truth tables of the circuits are shown below.

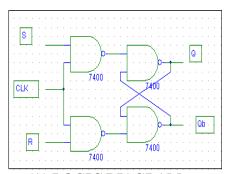

A clocked S-R flip-flop has an additional clock input so that the S and R inputs are active only when the clock is high. When the clock goes low, the state of flip-flop is latched and cannot change until the clock goes high again. Therefore, the clocked S-R flip-flop is also called "enabled" S-R flip-flop.

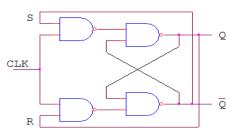

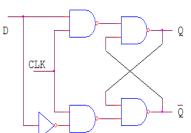

A D latch combines the S and R inputs of an S-R latch into one input by adding an inverter. When the clock is high, the output follows the D input, and when the clock goes low, the state is latched.

A S-R flip-flop can be converted to T-flip flop by connecting S input to Qb and R to Q.

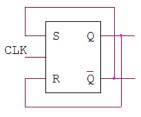

#### 1) S-R LATCH:

(A) LOGIC DIAGRAM

**(B) SYMBOL**

| S | R | Q+ | $\overline{Q}$ b+ |

|---|---|----|-------------------|

| 0 | 0 | Q  | $\overline{Q}$ b  |

| 0 | 1 | 0  | 1                 |

| 1 | 0 | 1  | 0                 |

| 1 | 1 | 0* | 0*                |

## $\overline{SR}$ LATCH:

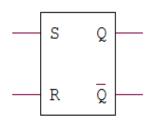

## 2) SR FLIP FLOP:

### **CIRCUIT DIAGRAM:**

## (A) LOGIC DIAGRAM

# \_\_\_\_\_S Q \_\_\_\_ \_\_\_\_R \_\_Q \_\_\_\_

(B) SYMBOL

|   | TRUTH TABLE |    |                   |  |  |  |  |  |  |  |

|---|-------------|----|-------------------|--|--|--|--|--|--|--|

| S | R           | Q+ | $\overline{Q}$ b+ |  |  |  |  |  |  |  |

| 0 | 0           | Q  | $\overline{Q}$ b  |  |  |  |  |  |  |  |

| 0 | 1           | 0  | 1                 |  |  |  |  |  |  |  |

| 1 | 0           | 1  | 0                 |  |  |  |  |  |  |  |

| 1 | 1           | 0* | 0*                |  |  |  |  |  |  |  |

#### **TRUTH TABLE**

| S | R | Q+ | $\overline{Q}$ b+ |

|---|---|----|-------------------|

| 0 | 0 | 1* | 1*                |

| 0 | 1 | 1  | 0                 |

| 1 | 0 | 0  | 1                 |

| 1 | 1 | Q  | $\overline{Q}$ b  |

## 3) CONVERSION OF SR-FLIP FLOP TO T-FLIP FLOP (Toggle)

## LOGIC DIAGRAM

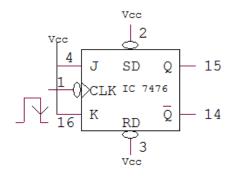

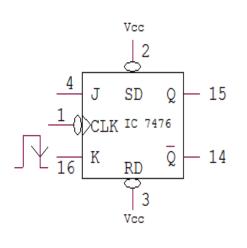

#### **T FLIP FLOP USING IC 7476**

#### SYMBOL

**TRUTH TABLE**

| Т | Qn + 1 |

|---|--------|

| 0 | Qn     |

| 1 | Qn     |

**SYMBOL**

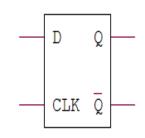

#### 4) CONVERSION OF SR-FLIP FLOP TO D-FLIP FLOP :

**D FLIP FLOP USING IC 7476**

#### **TRUTH TABLE**

| CLOCK | D | Q+ | <del>Q+</del> |

|-------|---|----|---------------|

| 0     | Х | Q  | Q             |

| 1     | 0 | 0  | 1             |

| 1     | 1 | 1  | 0             |

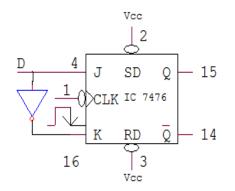

## 5. CONVERSION OF SR-FLIP FLOP TO JK-FLIP FLOP LOGIC DIAGRAM TRUTH TABLE

| Clock | J | K | Q+ | Q'+ | Comment      |

|-------|---|---|----|-----|--------------|

| 1     | 0 | 0 | Q  | Q'  | No<br>Change |

| 1     | 0 | 1 | 0  | 1   | Reset        |

| 1     | 1 | 0 | 1  | 0   | Set          |

| 1     | 1 | 1 | Q' | Q   | Toggle       |

## LOGIC DIAGRAM

| SD | RD | Clock | J           | K | Q  | Q' | Comment |  |  |

|----|----|-------|-------------|---|----|----|---------|--|--|

| 0  | 0  |       | Not Allowed |   |    |    |         |  |  |

| 0  | 1  | Х     | X           | X | 1  | 0  | Set     |  |  |

| 1  | 0  | Х     | X           | X | 0  | 1  | Reset   |  |  |

| 1  | 1  | 1     | 0           | 0 | NC | NC | Memory  |  |  |

| 1  | 1  | 1     | 0           | 1 | 0  | 1  | Reset   |  |  |

| 1  | 1  | 1     | 1           | 0 | 1  | 0  | Set     |  |  |

| 1  | 1  | 1     | 1           | 1 | Q' | Q  | Toggle  |  |  |

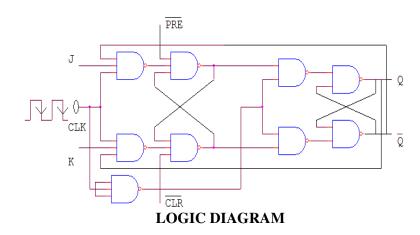

## 6. JK MASTER SLAVE FLIP FLOP

| PRE = | CLR = 1 |

|-------|---------|

| Clock | J | K | Q+ Q'+      |    | Comment      |  |  |  |  |

|-------|---|---|-------------|----|--------------|--|--|--|--|

| 1     | 0 | 0 | Q           | Q' | No<br>Change |  |  |  |  |

| 1     | 0 | 1 | 0 1         |    | Reset        |  |  |  |  |

| 1     | 1 | 0 | 1           | 0  | Set          |  |  |  |  |

| 1     | 1 | 1 | Race Around |    |              |  |  |  |  |

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base. ٠

- Make connections as shown in the circuit diagram.

- Verify the Truth Table and observe the outputs.

#### **VIVA QUESTIONS:**

- 1. What is the difference between Flip-Flop & latch?

- 2. Give examples for synchronous & asynchronous inputs?

- 3. What are the applications of different Flip-Flops?

- 4. What is the advantage of Edge triggering over level triggering?

- 5. What is the relation between propagation delay & clock frequency of flip-flop?

- 6. What is race around in flip-flop & how to over come it?

- 7. Convert the J K Flip-Flop into D flip-flop and T flip-flop?

- 8. List the functions of asynchronous inputs?

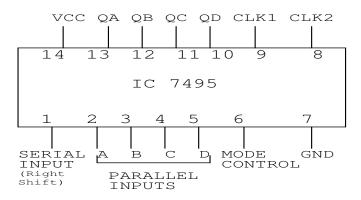

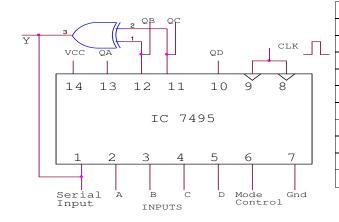

## EXPERIMENT: 13 SHIFT REGISTERS

AIM: To realize and study of Shift Register.

- 1) SISO (Serial in Serial out)

- 2) SIPO (Serial in Parallel out)

- 3) PIPO (Parallel in Parallel out)

- 4) PISO (Parallel in Serial out)

COMPONENTS REQUIRED: IC 7495, Patch Cords & IC Trainer Kit.

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Verify the Truth Table and observe the outputs.

## 1) SERIAL IN SERIAL OUT (SISO) (Right Shift)

| Serial<br>i/p<br>data | Shift<br>Pulses | QA | Q <sub>B</sub> | Qc | Q <sub>D</sub> |

|-----------------------|-----------------|----|----------------|----|----------------|

| -                     | -               | Х  | Х              | Х  | Х              |

| 0                     | t1              | 0  | Х              | Х  | Х              |

| 1                     | t2              | 1  | 0              | Х  | Х              |

| 0                     | t3              | 0  | 1              | 0  | Х              |

| 1                     | t4              | 1  | 0              | 1  | 0              |

| Х                     | t5              | Х  | 1              | 0  | 1              |

| X                     | t6              | Х  | Х              | 1  | 0              |

| Х                     | t7              | Х  | Х              | Х  | 1              |

| Х                     | t8              | Х  | Х              | Х  | Х              |

## 2) SERIAL IN PARALLEL OUT (SIPO)

| Serial<br>i/p data | Shift<br>Pulses | QA | Q <sub>B</sub> | Q <sub>C</sub> | QD |

|--------------------|-----------------|----|----------------|----------------|----|

| -                  | -               | Х  | Х              | Х              | Х  |

| 0                  | t1              | 0  | Х              | Х              | Х  |

| 1                  | t2              | 1  | 0              | Х              | Х  |

| 0                  | t3              | 0  | 1              | 0              | Х  |

| 1                  | t4              | 1  | 0              | 1              | 0  |

## 3) PARALLEL IN PARALLEL OUT (PIPO)

| Clock<br>Input<br>Terminal | Shift<br>Pulses | Q <sub>A</sub> | Q <sub>B</sub> | Q <sub>C</sub> | Q <sub>D</sub> |

|----------------------------|-----------------|----------------|----------------|----------------|----------------|

| -                          | -               | Х              | Х              | Х              | Х              |

| CLK <sub>2</sub>           | t1              | 1              | 0              | 1              | 0              |

## 4) PARALLEL IN SERIAL OUT (PISO)

| Clock<br>Input<br>Terminal | Shift<br>Pulses | Q <sub>A</sub> | Q <sub>B</sub> | Q <sub>C</sub> | Q <sub>D</sub> |

|----------------------------|-----------------|----------------|----------------|----------------|----------------|

| -                          | -               | Х              | Х              | Х              | Х              |

| CLK <sub>2</sub>           | t1              | 1              | 0              | 1              | 0              |

| CLK <sub>2</sub>           | t2              | Х              | 1              | 0              | 1              |

| 0                          | t3              | Х              | Х              | 1              | 0              |

| 1                          | t4              | Х              | X              | X              | 1              |

| X                          | t5              | Х              | Х              | Х              | Х              |

**<u>RESULT</u>**: The various operations of a shift register is verified

## EXPERIMENT: 14 SEQUENCE GENERATOR

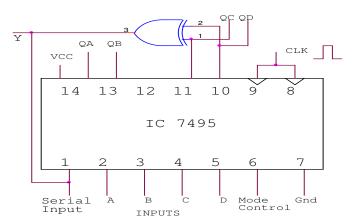

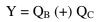

AIM: Design and set up a Sequence Generator using IC 7495.

COMPONENTS REQUIRED: IC 7495, IC 7486, Patch Cords & IC Trainer Kit.

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- By Keeping mode=1. Load the input A,B,C,D as in Truth Table 1<sup>st</sup> Row and give a clock pulse

- For count mode make mode = 0.

- Verify the Truth Table and observe the outputs.

DESIGN 1: Sequence = 100010011010111 Sequence length S = 15

| Y | = | Q <sub>C</sub> | (+) | $Q_D$ |

|---|---|----------------|-----|-------|

|---|---|----------------|-----|-------|

| Q <sub>A</sub> | Q <sub>B</sub> | Q <sub>C</sub> | QD | Y |

|----------------|----------------|----------------|----|---|

| 1              | 1              | 1              | 1  | 0 |

| 0              | 1              | 1              | 1  | 0 |

| 0              | 0              | 1              | 1  | 0 |

| 0              | 0              | 0              | 1  | 1 |

| 1              | 0              | 0              | 0  | 0 |

| 0              | 1              | 0              | 0  | 0 |

| 0              | 0              | 1              | 0  | 1 |

| 1              | 0              | 0              | 1  | 1 |

| 1              | 1              | 0              | 0  | 0 |

| 0              | 1              | 1              | 0  | 1 |

| 1              | 0              | 1              | 1  | 0 |

| 0              | 1              | 0              | 1  | 1 |

| 1              | 0              | 1              | 0  | 1 |

| 1              | 1              | 0              | 1  | 1 |

| 1              | 1              | 1              | 0  | 1 |

|                | 1              | 1              | 1  |   |

|                |                | 1              | 1  |   |

|                |                |                | 1  |   |

| X | 1 | 0 | 1 |

|---|---|---|---|

| 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 |

#### DESIGN 2: Sequence = 1001011 Sequence length S = 7

| Q <sub>A</sub> | $Q_{B}$ | Q <sub>C</sub> | $Q_{\rm D}$ | Y |

|----------------|---------|----------------|-------------|---|

| 1              | 1       | 1              | 1           | 0 |

| 0              | 1       | 1              | 1           | 0 |

| 0              | 0       | 1              | 1           | 1 |

| 1              | 0       | 0              | 1           | 0 |

| 0              | 1       | 0              | 0           | 1 |

| 1              | 0       | 1              | 0           | 1 |

| 1              | 1       | 0              | 1           | 1 |

|                | 1       | 1              | 0           |   |

|                |         | 1              | 1           |   |

|                |         |                | 1           |   |

|                |         |                |             |   |

| X | X | 1 | X |

|---|---|---|---|

| 0 | X | 0 | X |

| X | 1 | X | 0 |

| X | 1 | X | 1 |

DESIGN 3: Sequence = 1101011 Sequence length S = 7

$Y = Q_A + Q_C + Q_D$

| X | X | X | X |

|---|---|---|---|

| X | 1 | 1 | X |

| X | 1 | 0 | 1 |

| X | X | 0 | 1 |

| $Q_{\rm A}$ | $Q_{\rm B}$ | Q <sub>C</sub> | $Q_{\rm D}$ | Y |

|-------------|-------------|----------------|-------------|---|

| 1           | 1           | 1              | 1           | 1 |

| 1           | 1           | 1              | 1           | 0 |

| 0           | 1           | 1              | 1           | 1 |

| 1           | 0           | 1              | 1           | 0 |

| 0           | 1           | 0              | 1           | 1 |

| 1           | 0           | 1              | 0           | 1 |

| 1           | 1           | 0              | 1           | 1 |

|             | 1           | 1              | 0           |   |

|             |             | 1              | 1           |   |

|             |             |                | 1           |   |

#### VIVA QUESTIONS:

- 1) What is the necessity for sequence generation?

- 2) What are PISO, SIPO, and SISO with respect to shift register?

- 3) Differentiate between serial data & parallel data

- 4) What is the significance of Mode control bit?

- 5) What is a ring counter?

- 6) What is a Johnson counter?

- 7) How many Flip-flops are present in IC 7495?

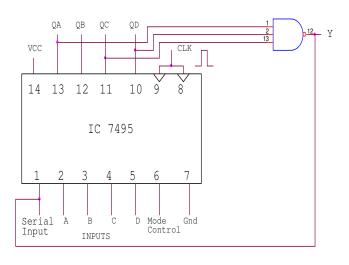

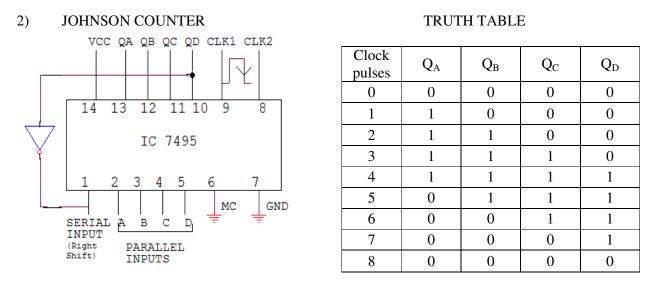

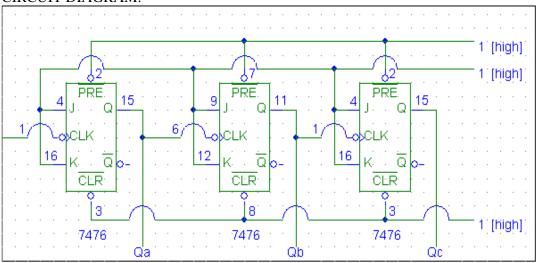

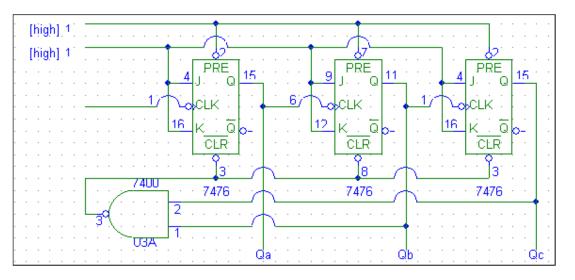

## EXPERIMENT: 15 RING COUNTER AND JOHNSON COUNTER

AIM: To realize and study Ring Counter and Johnson counter.

#### **LEARNING OBJECTIVE:**

- To learn about Ring Counter and its application

- To learn about Johnson Counter and its application

#### **COMPONENTS REQUIRED:**

IC 7495, IC 7404, Patch Cords & IC Trainer Kit.

#### THEORY:

Ring counter is a basic register with direct feedback such that the contents of the register simply circulate around the register when the clock is running. Here the last output that is  $Q_D$  in a shift register is connected back to the serial input.

A basic ring counter can be slightly modified to produce another type of shift register counter called Johnson counter. Here complement of last output is connected back to the not gate input and not gate output is connected back to serial input. A four bit Johnson counter gives 8 state output.

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.

- Make connections as shown in the circuit diagram.

- Apply clock to pin number 9 and observe the output

#### CIRCUIT DIAGRAM:

1) RING COUNTER

#### TRUTH TABLE

| Clock<br>pulses | Q <sub>A</sub> | Q <sub>B</sub> | Q <sub>C</sub> | Q <sub>D</sub> |

|-----------------|----------------|----------------|----------------|----------------|

| 0               | 1              | 0              | 0              | 0              |

| 1               | 0              | 1              | 0              | 0              |

| 2               | 0              | 0              | 1              | 0              |

| 3               | 0              | 0              | 0              | 1              |

| 4               | 1              | 0              | 0              | 0              |

| 5               | 0              | 1              | 0              | 0              |

| 6               | 0              | 0              | 1              | 0              |

| 7               | 0              | 0              | 0              | 1              |

| 8               | 1              | 0              | 0              | 0              |

<u>RESULT:</u> The truth table & working of Ring and Johnson counters is verified

## EXPERIMENT: 16 STUDY OF ASYNCHRONOUS COUNTER

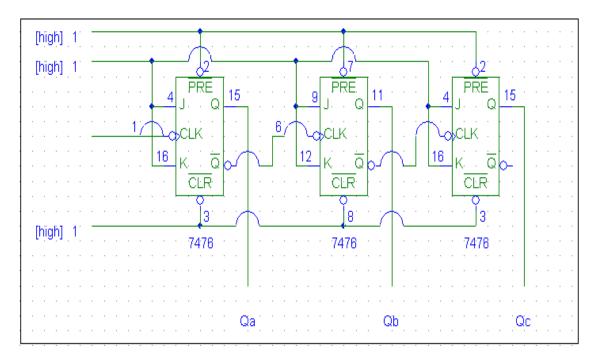

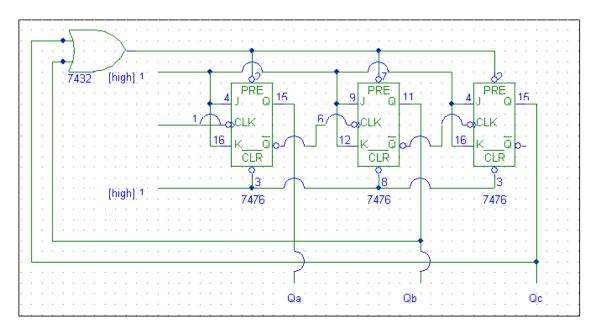

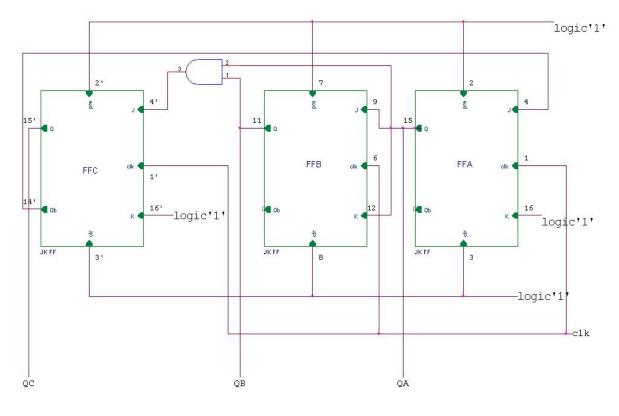

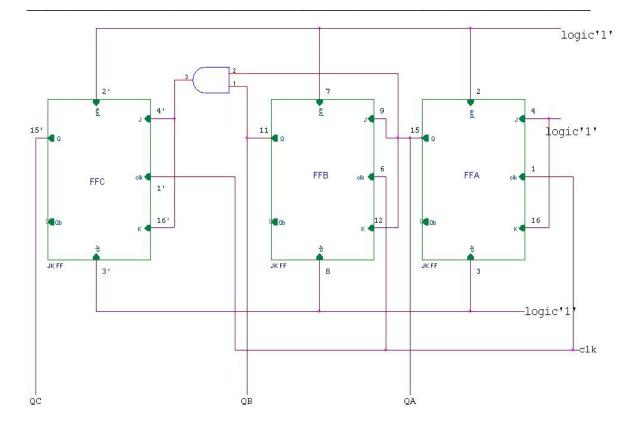

<u>AIM</u>: To design and test 3-bit binary asynchronous counter using flip-flop IC 7476 for the given sequence.

#### LEARNING OBJECTIVE:

- To learn about Asynchronous Counter and its application

- To learn the design of asynchronous up counter and down counter

#### COMPONENTS REQUIRED:

IC 7476, Patch Cords & IC Trainer Kit

#### THEORY:

A counter in which each flip-flop is triggered by the output goes to previous flip-flop. As all the flip-flops do not change state simultaneously spike occur at the output. To avoid this, strobe pulse is required. Because of the propagation delay the operating speed of asynchronous counter is low. Asynchronous counter are easy and simple to construct.

#### PROCEDURE:

- Check all the components for their working.

- Insert the appropriate IC into the IC base.