## LAB MANUAL

# SUBJECT: DIGITAL LOGIC DESIGN AND APPLICATIONS

SE (COMPUTERS) SEM III

## **INDEX**

| Sr.<br>No | Title of the Experiment                                 | Page<br>No. |

|-----------|---------------------------------------------------------|-------------|

| 1         | Study of BASIC Gates                                    | 3           |

| 2         | Universal Gates                                         | 6           |

| 3         | Study of Full & Half Adder & Subtractor using Gates     | 8           |

| 4         | Study of Magnitude Comparator                           | 10          |

| 5         | Study of Multiplexer                                    | 11          |

| 6         | Study of Demultiplexer                                  | 13          |

| 7         | Implementation of Flip-Flops using NAND & Study of 7476 | 15          |

| 8         | Study of Shift Register                                 | 17          |

| 9         | Design of Counter & Study of IC 7490                    | 19          |

| 10        | Vo V/S Vi Characteristic of TTL & CMOS                  | 21          |

#### EXPT. NO. 1

#### TITLE STUDY OF BASIC GATES

AIM To study basic gates.

**APPARATUS** Power Supply, Breadboard, Connecting wires.

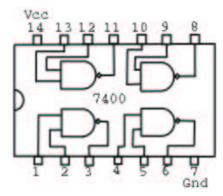

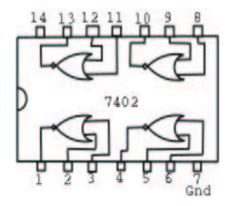

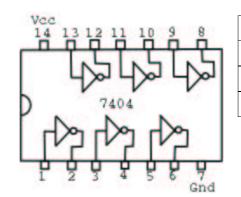

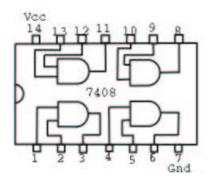

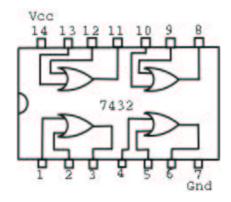

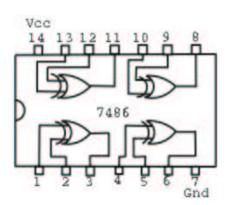

**COMPONENTS** ICs 7400, 7402, 7404, 7408, 7432, 7486, LED.

**IC PINOUTS**

#### **TRUTH-TABLE**

| NAND |   |       |  |  |

|------|---|-------|--|--|

| Α    | В | Y=A.B |  |  |

| 0    | 0 | 1     |  |  |

| 0    | 1 | 1     |  |  |

| 1    | 0 | 1     |  |  |

| 1    | 1 | 0     |  |  |

| NOR |                    |  |  |  |

|-----|--------------------|--|--|--|

| В   | Y=A+B              |  |  |  |

| 0   | 1                  |  |  |  |

| 1   | 0                  |  |  |  |

| 0   | 0                  |  |  |  |

| 1   | 0                  |  |  |  |

|     | <b>B</b><br>0<br>1 |  |  |  |

| NOT |     |  |  |

|-----|-----|--|--|

| Α   | Y=A |  |  |

| 0   | 1   |  |  |

| 1   | 0   |  |  |

| AND |   |       |  |  |

|-----|---|-------|--|--|

| Α   | В | Y=A.B |  |  |

| 0   | 0 | 0     |  |  |

| 0   | 1 | 0     |  |  |

| 1   | 0 | 0     |  |  |

| 1   | 1 | 1     |  |  |

| OR |                    |  |  |

|----|--------------------|--|--|

| В  | Y=A+B              |  |  |

| 0  | 0                  |  |  |

| 1  | 1                  |  |  |

| 0  | 1                  |  |  |

| 1  | 1                  |  |  |

|    | <b>B</b><br>0<br>1 |  |  |

| EX-OR                                                                                                                  |   |   |  |  |

|------------------------------------------------------------------------------------------------------------------------|---|---|--|--|

| $\mathbf{A} \qquad \mathbf{B} \qquad \mathbf{Y} = \mathbf{A} \mathbf{\overline{B}} + \mathbf{\overline{A}} \mathbf{B}$ |   |   |  |  |

| 0                                                                                                                      | 0 | 0 |  |  |

| 0                                                                                                                      | 1 | 1 |  |  |

| 1                                                                                                                      | 0 | 1 |  |  |

| 1                                                                                                                      | 1 | 1 |  |  |

| THEORY    | Logic gates are the digital circuits with one output and one or<br>more inputs. They are the basic building blocks of any logic ckt.<br>Different logic gates are : <b>AND, OR, NOT, NAND, NOR, EX-OR.</b> They work according to certain logic.<br><b>AND</b> : Logic eqn. $Y = A.B$<br>The output of AND gate is true when the inputs A and B are<br>True.<br><b>OR</b> : Logic eqn. $Y = A+B$ .<br>The output of OR gate is true when one of the inputs A and B or<br>both the inputs are true.<br><b>NOT</b> : Logic eqn. $Y = \overline{A}$ .<br>The output of NOT gate is complement of the input.<br><b>NAND</b> : Logic eqn. $Y = \overline{A}.B$<br>The output of NAND gate is true when one of the inputs or both<br>the inputs are low level.<br><b>NOR</b> : Logical eqn. $Y = \overline{A}+B$ .<br>The output of NOR gate is true when both the inputs are low.<br><b>EX-OR</b> : Logic eqn. $Y = \overline{AB}+\overline{AB}$ .<br>The output of NOR gate is true when both the inputs are low. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROCEDURE | <ol> <li>1)Give biasing to the IC and do necessary connections.</li> <li>2) Give various combinations of inputs and note down the output with help of LED for all gate ICs one by one.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

**CONCLUSION** Thus all basic gates are studied.

#### EXPT. NO. 2

TITLE **UNIVERSAL GATES**

To study the realization of basic gates using universal gates. AIM

**APPARATUS** Power supply, Breadboard.

COMPONENTS ICs 7400, 7402, LED.

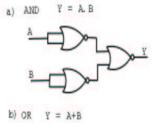

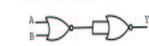

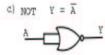

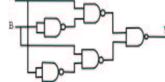

CIRCUIT DIAGRAM Using NAND

Using NOR

¥ = A. B

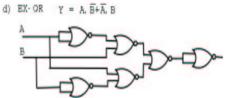

d) EX-OR  $Y = \overline{A}, B+A, \overline{B}$

e) NOR  $Y = \overline{A+B}$

o/p of

C) NOT Y = A

Y

e) NAND Y = A.B

- THEORY

AND, OR, NOT are called basic gates as their logical operation cannot be simplified further.

NAND and NOR are called universal gates as using only NAND or only NOR any logic function can be implemented. Using NAND and NOR gates and De Morgans Theorems different basic gates & EX-OR gates are realized.

- **PROCEDURE** 1)Give biasing to the IC and do necessary connections as shown in the ckt. diagram.

2)Give various combinations of inputs and notedown output using LED.

3) Repeat the procedure for all gates.

### OBSERVATION TABLE

| Α | В | Y |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

**CONCLUSION** Thus universal gates are studied.

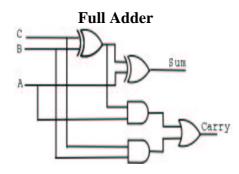

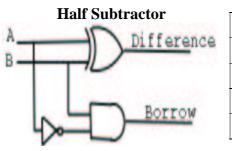

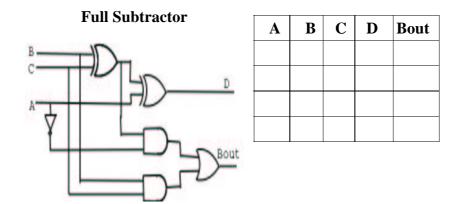

#### EXPT. NO. 3

TITLE ADDER AND SUBTRACTOR

**AIM** To study adder and subtractor circuits using logic gates.

**APPARATUS** Power supply, breadboard.

COMPONENTS

ICs 7486, 7432, 7408, 7404, LEDs.

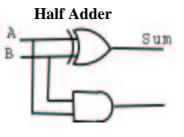

CIRCUIT DIAGRAM AND OBSREVATION TABLE

| A | B | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 |     |       |

| 0 | 1 |     |       |

| 1 | 0 |     |       |

| 1 | 1 |     |       |

| A | B | С | Sum | Carry |

|---|---|---|-----|-------|

|   |   |   |     |       |

|   |   |   |     |       |

|   |   |   |     |       |

|   |   |   |     |       |

| Α | В | Diff. | Bout |

|---|---|-------|------|

|   |   |       |      |

|   |   |       |      |

|   |   |       |      |

|   |   |       |      |

- **THEORY** A digital adder circuit adds binary signals & a subtractor subtracts binary signals. Half Adder/Subtractor is a basic ckt. that adds / subtracts 2 bits and generates sum or difference along with Carry / Borrow. Unlike half adder or subtractor a full adder / subtractor has the provision to take consideration of previous carry / borrow also.

- **PROCEDURE** A digital adder circuit adds binary signals & a subtractor subtracts binary signals. Half Adder / subtractor is a basic ckt. that adds / subtracts 2 bits and generates sum or difference along with Carry / Borrow. Unlike half adder or subtractor a full adder / subtractor has the provision to take consideration of previous carry / borrow also.

- **CONCLUSION** Thus half & full Adder / Subtractor is studied.

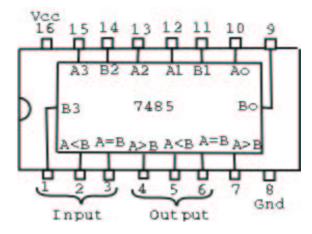

#### EXPT. NO. 4

TITLE MAGNITUDE COMPARATOR

AIM To study magnitude comparator.

**APPARATUS** Power supply, Breadboard.

COMPONENTS IC 7485, LEDs.

**IC PINOUT**

- **THEORY** Magnitude Comparator compares two binary data signals A & B and generates the results of comparision in form of three output signals A>B, A=B, A<B. IC 7485 is a 4-bit comparator. The cascade inputs A>B, A=B, A<B can be used to construct a comparator comparing more than 4 bits. The compare outputs depend on both compare i/ps as well as cascade i/ps.

- PROCEDURE 1)Give biasing to the IC .

2)Give various two 4-bit inputs and note down output.

3)Do connections for cascading and note down output for various two 8-bit inputs.

## OBSERVATION TABLE

#### **For 4-bit Comparator**

| <b>A</b> 3 | A2 | Aı | Ao | <b>B</b> 3 | <b>B</b> 2 | <b>B</b> 1 | Bo | A>B | A=B | A <b< th=""></b<> |

|------------|----|----|----|------------|------------|------------|----|-----|-----|-------------------|

|            |    |    |    |            |            |            |    |     |     |                   |

|            |    |    |    |            |            |            |    |     |     |                   |

|            |    |    |    |            |            |            |    |     |     |                   |

|            |    |    |    |            |            |            |    |     |     |                   |

|            |    |    |    |            |            |            |    |     |     |                   |

|            |    |    |    |            |            |            |    |     |     |                   |

CONCLUSION

Thus magnitude comparator is studied.

#### EXPT. NO. 5

TITLE MULTIPLEXER

AIM To study multiplexer.

**APPARATUS** Power supply, Breadboard.

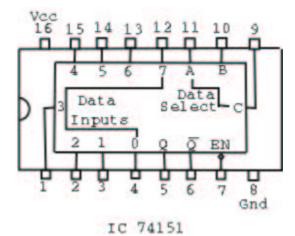

**COMPONENTS** IC 74151, LEDs.

**IC PINOUT**

THEORY Multiplexer is a combinational ckt. that is one of the most widely used in digital design. The multiplexer is a data selector which gates one out of several i/ps to a single o/p. It has n data i/ps & one o/p line & m select lines where  $2^{m} = n$ . Depending upon the digital code applied at the select inputs one out of n data input is selected & transmitted to a single o/p channel. Normally strobe(G) input is incorporated which is generally active low which enables the multiplexer when it is LOW. Strobe i/p helps in cascading. A 4:1 Mux. using NAND gate can be designed as shown in dgm 1. No. of ICs are available such as 74157, 74158 (Quad 2:1 mux), 74352, 74153 (dual 4:1 Mux.), 74151A, 74152 (8:1 Mux.), 74150 (16:1 Mux). IC 74151A is a 8:1 multiplexer which provides two complementary o/ps Y &  $\overline{Y}$ . The o/p Y is same as the selected i/p & Y is its complement. The n:1 multiplexer can be used to realize a m variable function. (2<sup>m</sup> = n, m is no. of select inputs)

**PROCEDURE**1)Give biasing to the IC.<br/>2)Do necessary connections.

| <b>OBSERVATION</b> |        | Inpu | Outputs |        |   |   |

|--------------------|--------|------|---------|--------|---|---|

| TABLE              | Select |      |         | Strobe |   |   |

|                    | С      | В    | Α       | S      | Q | Q |

|                    |        |      |         |        |   |   |

|                    |        |      |         |        |   |   |

|                    |        |      |         |        |   |   |

|                    |        |      |         |        |   |   |

|                    |        |      |         |        |   |   |

**CONCLUSION** Thus multiplexer is studied.

ASSIGNMENT

- Verify the truthtable of IC 74151, 8:1 Mux.

Connect two 74151 ICs in cascading & verify its operation as a 16:1 Mux.

- 3)Implement the function  $Y = A\overline{B} + BC$  using 74151 & verify the truthtable.

#### EXPT. NO. 6 DEMULTIPLEXER

AIM To study demultiplexer.

**APPARATUS** Power supply, Breadboard.

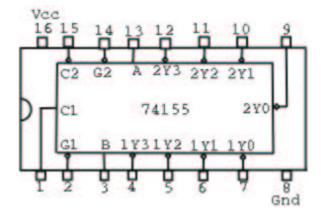

COMPONENTS IC 74155, LEDs.

**IC PINOUT**

TITLE

THEORY Demux takes single i/p & distributes it over several o/ps. It has one data line, n o/p lines & m select lines where  $2^{m} = n$ . The logic ckt. of 1:4 demux. using NAND gates is shown in the dgm 1. The ckt. can also be used as binary to decimal decoder with binary inputs applied at the select i/p lines & o/p will be obtained on the corresponding line. MSI ICs available in TTL family for demux. are 74138(3 line to 8 line decoder/demux.), 74139(dual 2 to 4 line decoder/driver.), 74154(4 to 16 line decoder/demux), 74155(dual 2 to 4 line decoder) etc. IC 74155 is a dual 2 to 4 line decoder. It has two sets of active low outputs 1Y0 to 1Y3 & 2Y0 to 2Y3. A & B are the select terminals common for both the demux. C1, C2 & G1, G2 are the data lines & strobe(enable) inputs for the two demux. C1 is active high, C2, G1, G2 are active low. The two 2 line to 4 line demux. can be combined to implement 3 line to 8 line demux.

**PROCEDURE** 1)Give biasing to the IC. 2)Do necessary connections.

#### OBSERVATION 2-Line to 4-Line Decoder OR 1-Line to 4-Line Demultiplexer TABLE Inputs Outputs

|     |     | Inputs |             | Outputs |                        |                 |     |  |

|-----|-----|--------|-------------|---------|------------------------|-----------------|-----|--|

| Sel | ect | Strobe | Strobe Data |         | <b>1Y</b> 1            | 1Y2             | 1Y3 |  |

| В   | A   | G1/G2  | C1/C2       | 2Y0     | <b>2Y</b> <sub>1</sub> | 2Y <sub>2</sub> | 2Y3 |  |

|     |     |        |             |         |                        |                 |     |  |

|     |     |        |             |         |                        |                 |     |  |

|     |     |        |             |         |                        |                 |     |  |

|     |     |        |             |         |                        |                 |     |  |

|     |     |        |             |         |                        |                 |     |  |

#### **3:8 Decoder OR 1:8 Demultiplexer**

|                         | Inputs |   |    |     | Outputs |     |     |     |             |     |     |

|-------------------------|--------|---|----|-----|---------|-----|-----|-----|-------------|-----|-----|

| Select Strobe<br>(Data) |        |   |    |     |         |     |     |     |             |     |     |

| $\mathbf{C}^{+}$        | B      | A | G‡ | 2Y0 | 2Y1     | 2Y2 | 2Y3 | 1Y0 | <b>1Y</b> 1 | 1Y2 | 1Y3 |

|                         |        |   |    |     |         |     |     |     |             |     |     |

|                         |        |   |    |     |         |     |     |     |             |     |     |

|                         |        |   |    |     |         |     |     |     |             |     |     |

|                         |        |   |    |     |         |     |     |     |             |     |     |

|                         |        |   |    |     |         |     |     |     |             |     |     |

$C_{*} = I/P$ 's C<sub>1</sub> and C<sub>2</sub> connected together

$G_{*} = I/P's G_1$  and  $G_2$  connected together

**CONCLUSION** Thus demultiplexer is studied.

**ASSIGNMENT** 1)Verify the operation of both the demux in IC 74155 as per the truthtable.

2)Combine the two demux to give 3 line to 8 line demux & verify

the operation.

#### EXPT. NO. 7

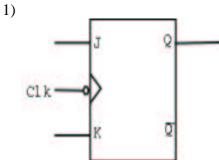

To study R-S, J-K, D and T flip-flops using IC 7476.

**APPARATUS** Breadboard, Power supply.

COMPONENTS ICs 7400, 7402, 7476, LED.

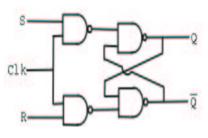

CIRCUIT DIAGRAM AND TRUTHTABLE

AIM

#### I) SR FF using NAND

| Clk | S | R | Qn |

|-----|---|---|----|

| 0   | Х | Х |    |

| 1   | 0 | 0 |    |

| 1   | 0 | 1 |    |

| 1   | 1 | 0 |    |

| 1   | 1 | 1 |    |

**II) JK FF (IC 7476)**

| Clk | J | K | Qn |

|-----|---|---|----|

|     | 0 | 0 |    |

|     | 0 | 1 |    |

|     | 1 | 0 |    |

|     | 1 | 1 |    |

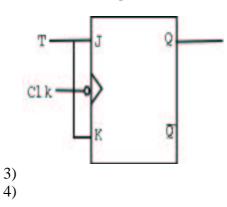

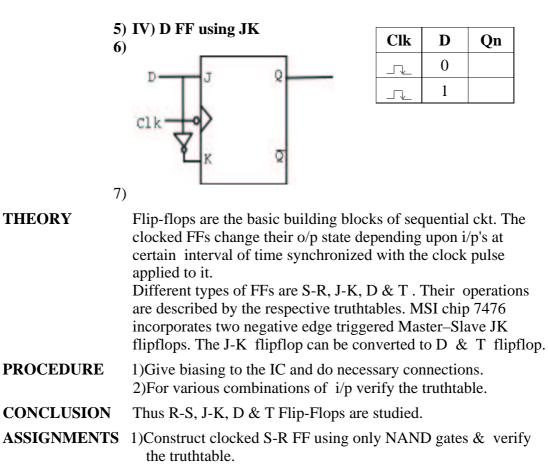

2) III) T FF using JK

| Clk | Т | Qn |

|-----|---|----|

|     | 0 |    |

|     | 1 |    |

2)Verify the truthtable of J-K FF using IC 7476. Observe the effect of Preset & Clear i/ps.

3)Convert the J-K FF to D & T FF.

#### EXPT. NO. 8 SHIFT REGISTER

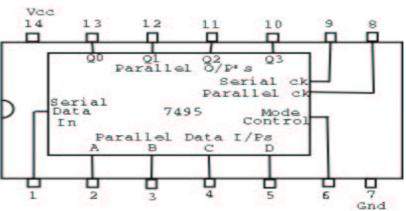

AIM To study shift registers. **APPARATUS COMPONENTS**

Power supply, Breadboard. IC 7495, LEDs.

**IC PINOUT**

TITLE

THEORY A flip-flop stores 1-bit of digital information. It is also referred to as 1-bit register. An array of flip-flops is required to store the no. of bits. This is called register. The data can be entered into or retrieved from the register. So depending on the way how the data can be entered or retrieved there are four possible modes of operation.

1)Serial in serial out (SISO)

2)Serial in parallel out (SIPO)

3)Parallel in serial out (PISO)

4)Parallel in parallel out (PIPO)

Registers can be designed using J-K or S-R as D-type flip-flops and are also available as MSI devices.

The register which can be operated in all possible modes & also the shifting of data is possible in both the directions is called Universal register.

**PROCEDURE** 1)Give biasing to the IC 2)Do connections for SIPO, PIPO & Left Shift and notedown corresponding o/p.

#### **OBSERVATIONS I) PIPO : Parallel I/P Parallel O/P**

|   | Μ | Clk2 | Α | В | С | D | QA | QB | Qc | Qd |

|---|---|------|---|---|---|---|----|----|----|----|

| Ī | 1 | 0    | Х | Х | Х | Х |    |    |    |    |

|   | 1 |      |   |   |   |   |    |    |    |    |

#### II)SIPO : Serial I/P Parallel O/P a) Shift Right

| Μ | Clk1 | Serial I/P | QA | QB | Qc | Qd |

|---|------|------------|----|----|----|----|

| 0 |      |            |    |    |    |    |

|   |      |            |    |    |    |    |

#### b) Shift Left

| Μ | Clk2 | D I/P | QA | QB | Qc | QD |

|---|------|-------|----|----|----|----|

| 1 |      |       |    |    |    |    |

|   |      |       |    |    |    |    |

**CONCLUSION** Thus shift register is studied.

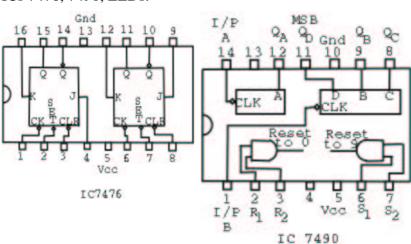

# EXPT. NO. 9TITLECOUNTERSAIMTo study the counters.APPARATUSPower supply, Breadboard.COMPONENTSICs 7476, 7490, LEDs.

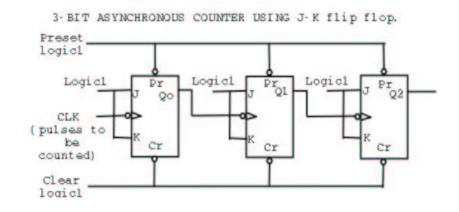

#### CIRCUIT DIAGRAM

**IC PINOUTS**

| THEORY    | A ckt. used for counting the pulses is known as counter.<br>Basically there are two types of counters.<br><b>1)Asynchronous counter (ripple counter).</b><br><b>2)Synchronous counter :</b> — In the case of an Asynchronous<br>Counter, all the flip-flops are not clocked simultaneously. This<br>counter is simple in operation & requires a min. of hardware.<br>But its speed is low. Each FF is triggered by a previous FF o/p.<br>Each FF takes its own time to give o/p (due to propagation<br>delay). So final settling time is high. They have the problem of<br>glitch.<br><b>Synchronous counter :</b> — In synchronous counters all the Ffs<br>are clocked simultaneously. It is complex in construction, but<br>speed is more. In this case since each FF is clocked<br>simultaneously thus settling time is the delay time of single FF.<br>No problem of glitch.<br><b>Asynchronous counter IC (7490) :</b> — It is a BCD counter. It<br>consists of four FFs internally connected to provide a mod-2<br>counter and a mod-5 counter. The mod-2 and mod-5 counters<br>can be used independently or in combination. FFA operates as<br>a mod2 counter whereas the combination of FFB, FFC and<br>FFD form a mod-5 counter. There are two reset inputs R1 &<br>R2 both of which are to be connected to logic 1 level for<br>clearing all the FFs. The two set inputs S1 & S2 when<br>connected to logic1 level are used for setting the counter to<br>1001. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROCEDURE | 1)Do connections as per the ckt. dgm.<br>2)Give biasing to the ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

2)Give biasing to the ICs.3)Observe o/p using LEDs.

#### **OBSERVATIONS**

| <b>Counter State</b> | Q <sub>0</sub> | <b>Q</b> 1 | Q2 |

|----------------------|----------------|------------|----|

| 0                    |                |            |    |

| :                    |                |            |    |

| :                    |                |            |    |

| 7                    |                |            |    |

**CONCLUSION** Thus counters is studied.

**EXPT. NO. 10** TITLE TRANSFER CHARACTERISTIC OF TTL AND CMOS AIM To study TTL & CMOS transfer characteristics. **APPARATUS** Dual Power supply, Breadboard, Multimeter. **COMPONENTS** ICs 74LS00, 74HC00. **CIRCUIT** 5v 5 **DIAGRAM** 2.4v21 Vac THEORY A group of compatible ICs with the same logic levels and supply voltages for performing various logic functions have been fabricated using a specific ckt. configuration which is referred to as a logic family. TTL (Transistor-Transistor logic) is one of the saturated Bipolar logic families. CMOS (Complementary metal oxide semiconductor) is an unipolar logic family. Various chars. of digital ICs are used to compare their performances. **Current & Voltage parameters :-**High level i/p voltage V<sub>IH</sub> :— This is the min. i/p voltage at the o/p corresponding to logic1. Low level i/p voltage  $V_{IL}$ :— This is the max. i/p voltage which is recognized by the gate as logic0. High level output voltage V<sub>OH</sub> :— This is the min. voltage available at the o/p corresponding to logic1. Low level o/p voltage V<sub>OL</sub> :— This is the max. voltage available at the o/p corresponding to logic0.

- PROCEDURE 1)Connect the ckt. as per ckt. dgm. for TTL IC.

2)Vary the i/p voltage in steps & notedown corresponding o/p voltage.

3)Plot graph of Vi Vs Vo.

- 4)Repeat same procedure for CMOS IC.

#### **OBSERVATIONS**

| Vi | Vo |  |

|----|----|--|

|    |    |  |

|    |    |  |

|    |    |  |

|    |    |  |

|    |    |  |

**CONCLUSION** Thus transfer characteristics of **TTL & CMOS** ICs is studied.